Altera 25G Ethernet IP 的 PMA 内部环回测试

本文主要介绍针对 25G Ethernet Altera FPGA IP 在 Darby Creek 板卡上的 PMA 内部环回测试。

Altera 25G Ethernet IP 介绍

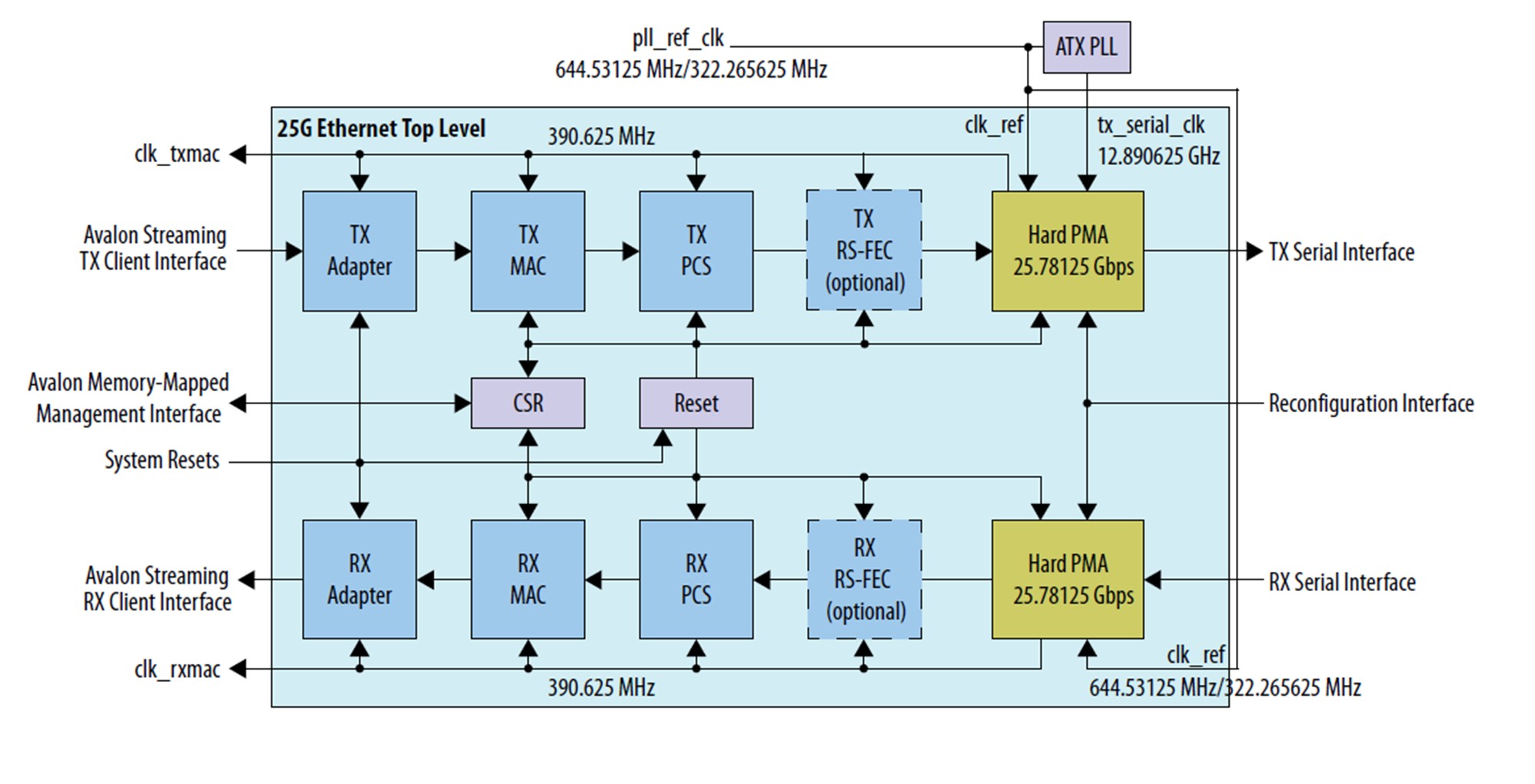

Altera 25 Gbps 以太网 (25GbE) IP 核实现了 25G 和 50G 以太网规范,即 25 千兆以太网联盟的 1.4 草案。此 IP 核包括一个选项,可支持 IEEE 802.3-2012 以太网标准条款 66 中定义的单向传输。25GbE IP 核的介质访问控制 (MAC) 客户端侧接口是一个 64 位 Avalon® Streaming 接口 (Avalon-ST)。它映射到一个 25.78125 Gbps 收发器。该 IP 核可选择包括 Reed-Solomon 前向纠错 (FEC),以支持直接连接铜缆 (DAC)。

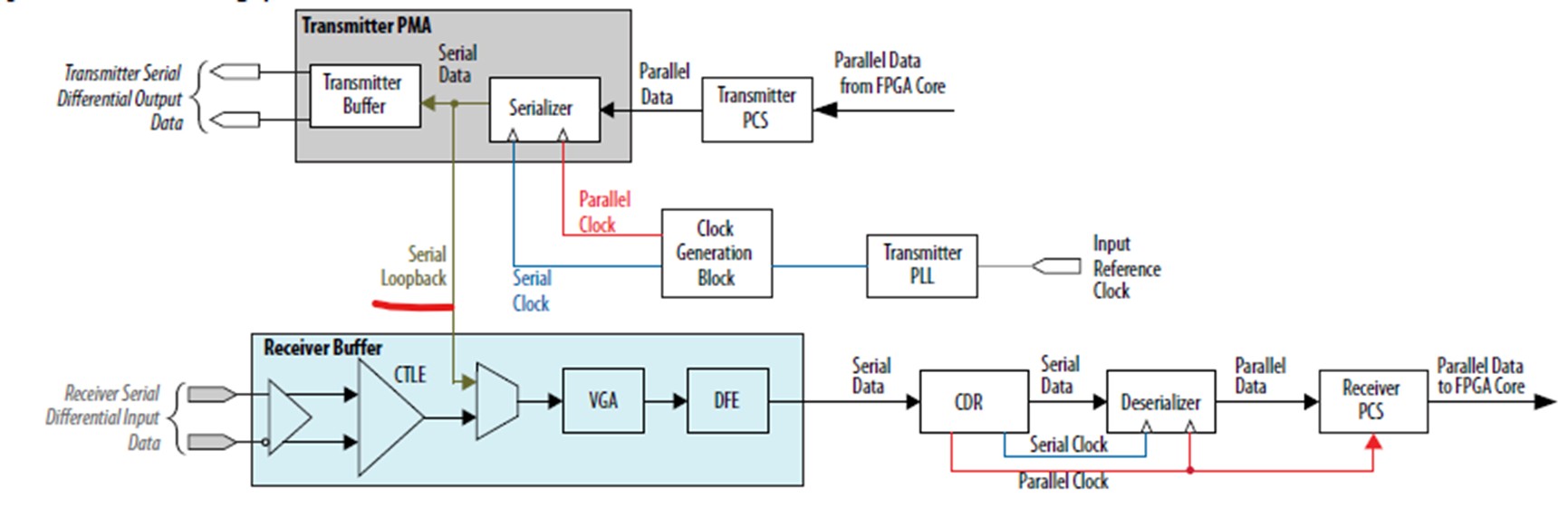

如下图 (图1) 所示,此 IP 核提供标准介质访问控制 (MAC) 和物理编码子层 (PCS) 和 PMA 功能。PHY 包含 PCS 和 PMA。所以,用户使用的时候只需要提供 ATX PLL 时钟源,即可实现完整的 25Gbps 以太网功能。

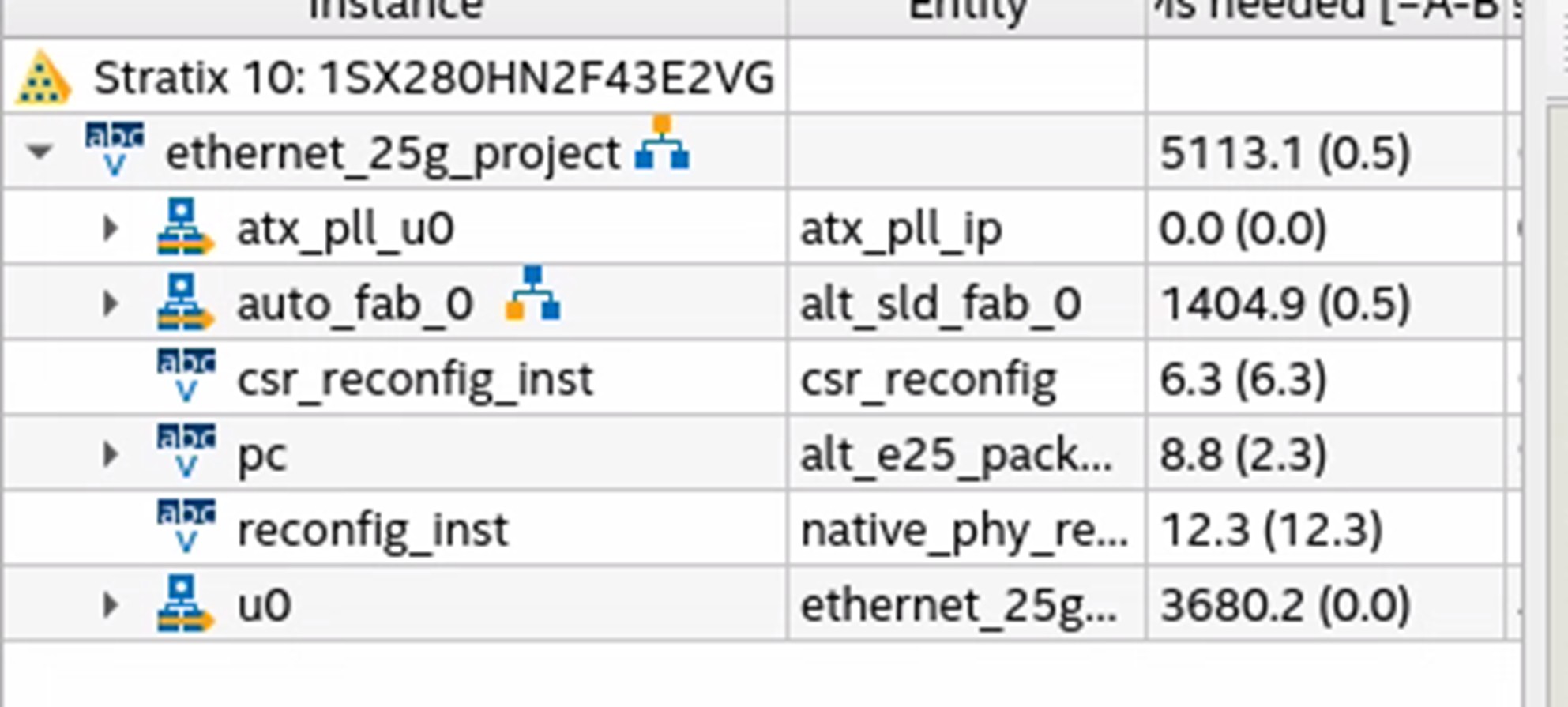

新建工程与参数配置

如下图 (图2) 所示,在 Quartus Prime 中新建工程,例化 25G Ethernet IP 核、ATX PLL 模块以及配置相关文件,整个工程结构如下:

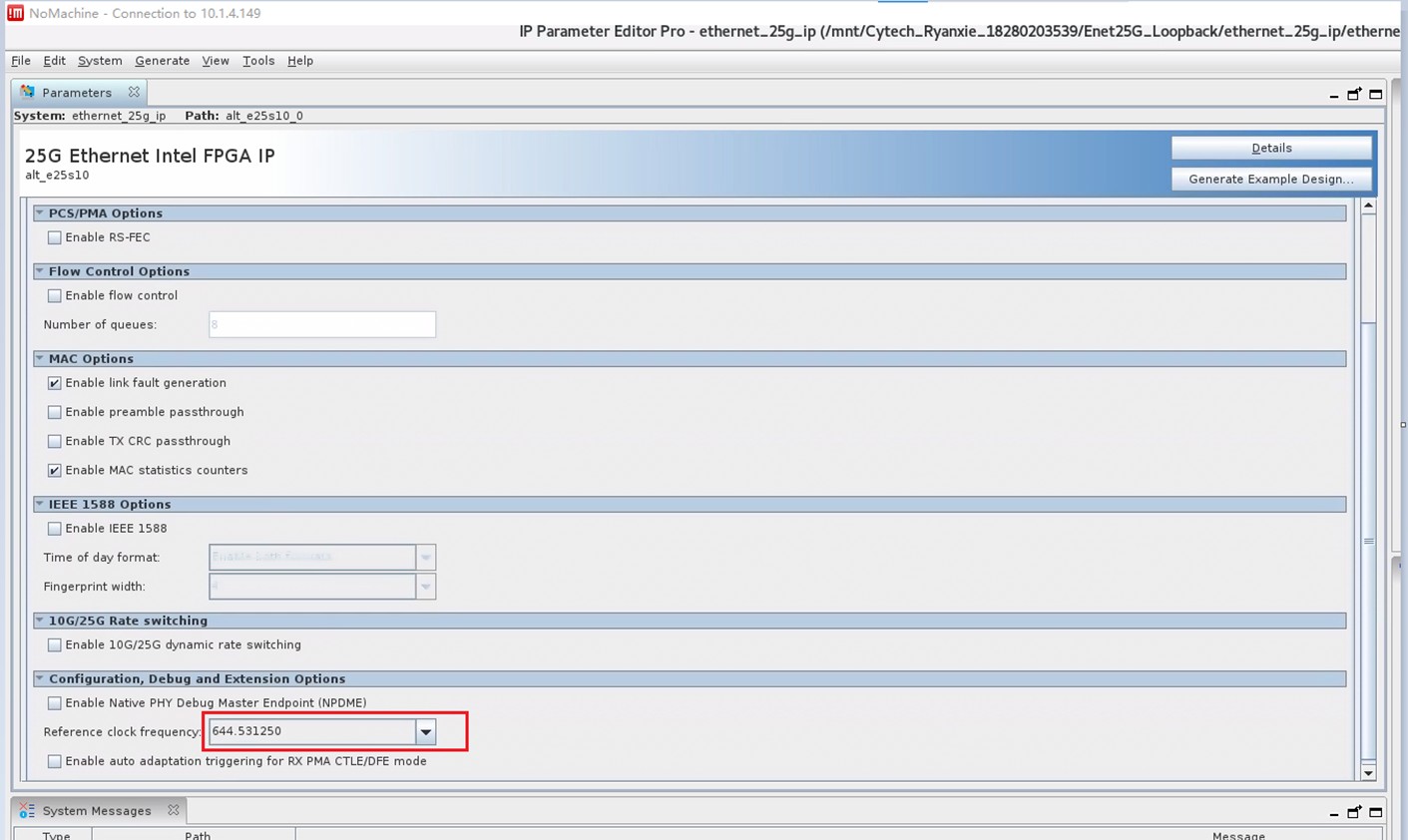

25G IP 设置如下图 (图3) 所示,参考时钟频率需要选择板上实际的时钟:644.53125M。

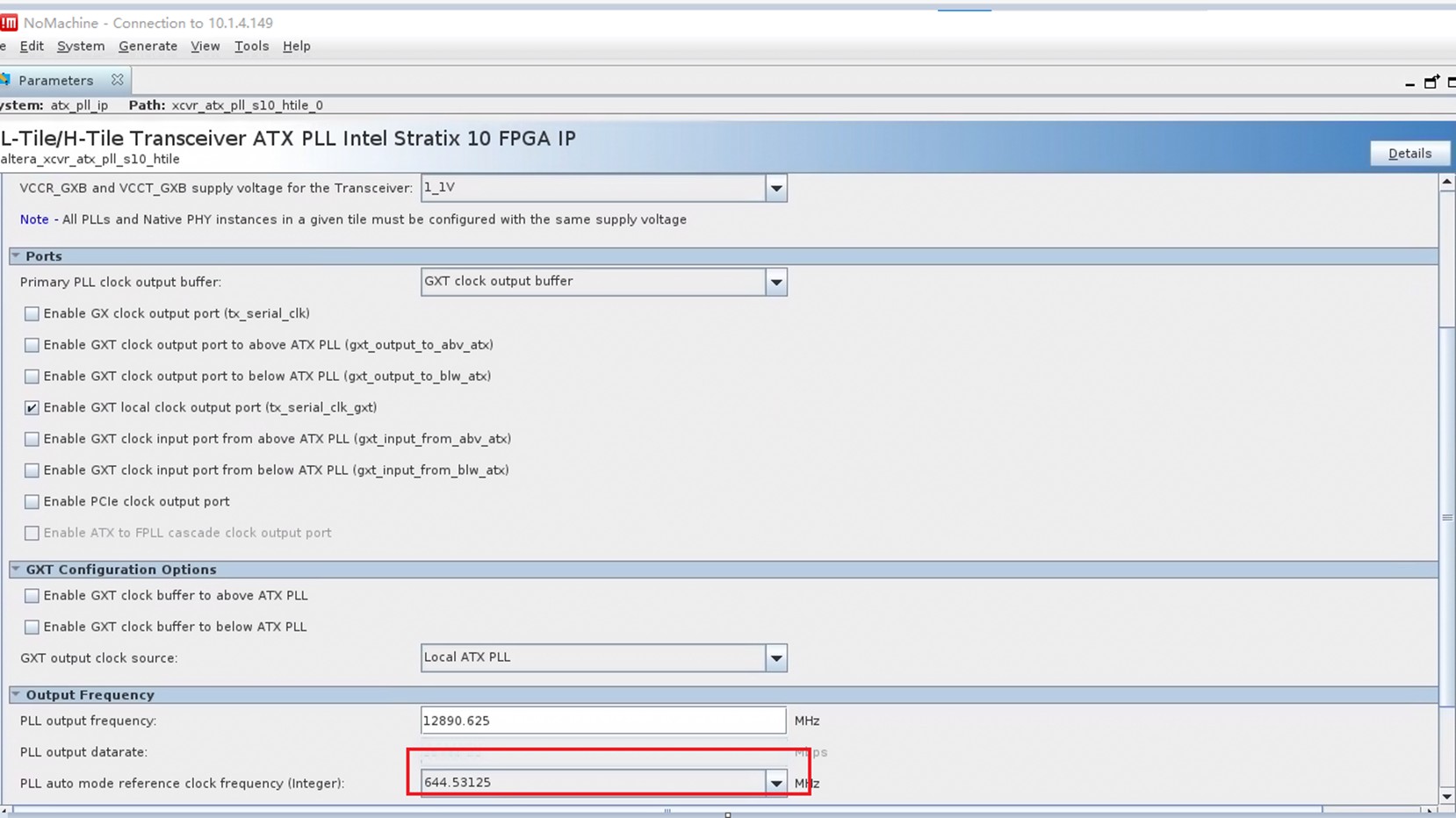

ATX PLL IP 设置如下图 (图4) 所示,参考时钟输入频率 644.53125M.PLL,输出频率为 12890.625M。

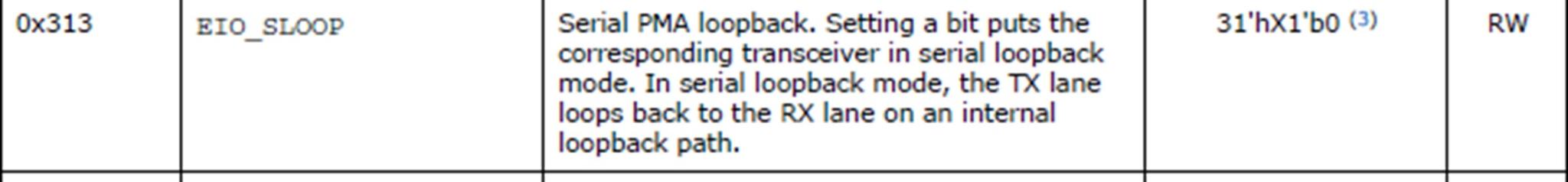

配置寄存器为 PMA 环回,Serial PMA loopback 环回位置如下图 (图5) 所示:

通过配置寄存器来使能 Serial PMA loopback,即把寄存器 0x313 的 bit[0] 置 1。

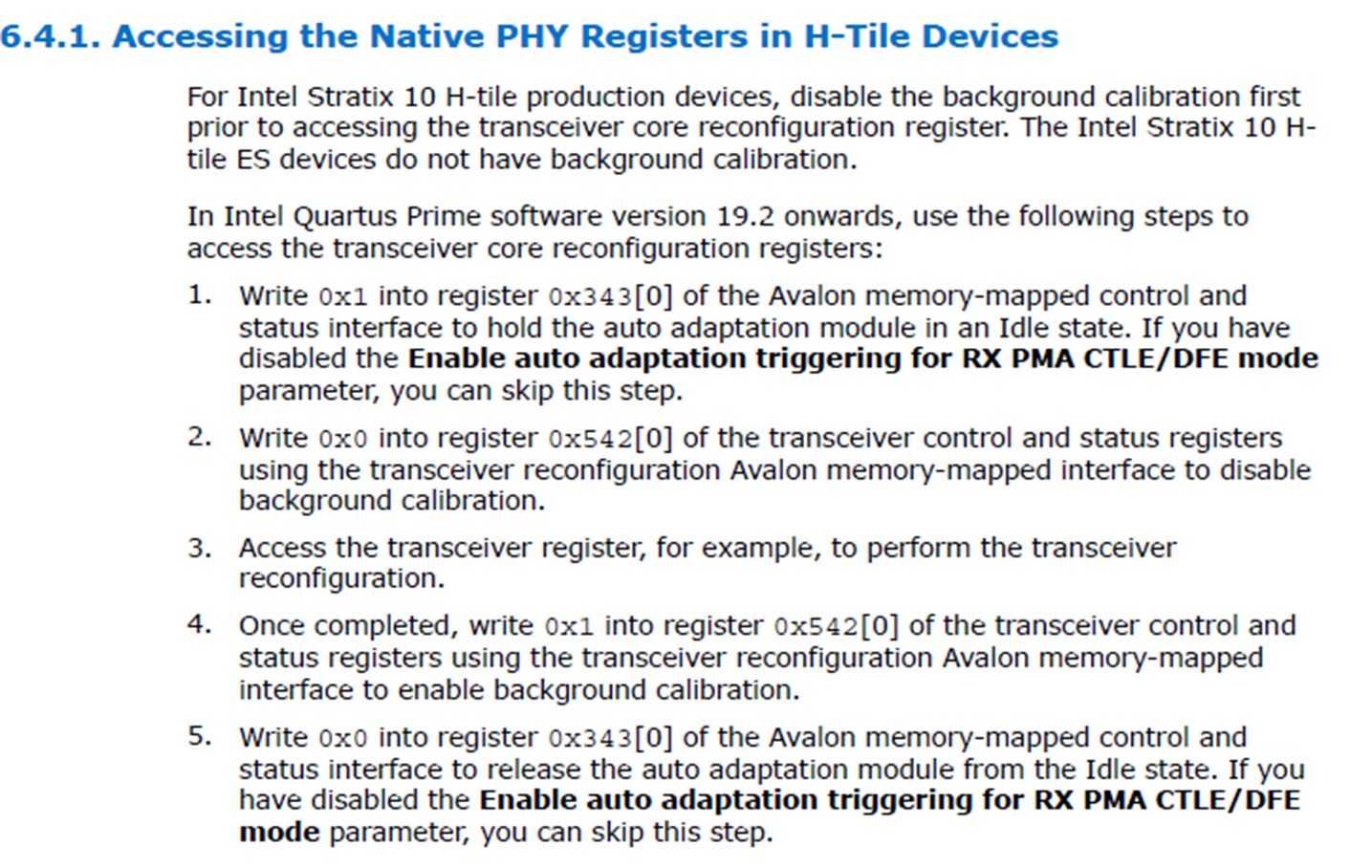

接下来按照 datasheet 里的配置寄存器的步骤执行步骤 2、3、4。0x343 通过 reconfig 总线来配置,而 0x542 需要通过 CSR 总线来配置。工程里通过“native_phy_reconfig.v”和“csr_reconfig.v”两个文件来完成寄存器的配置。

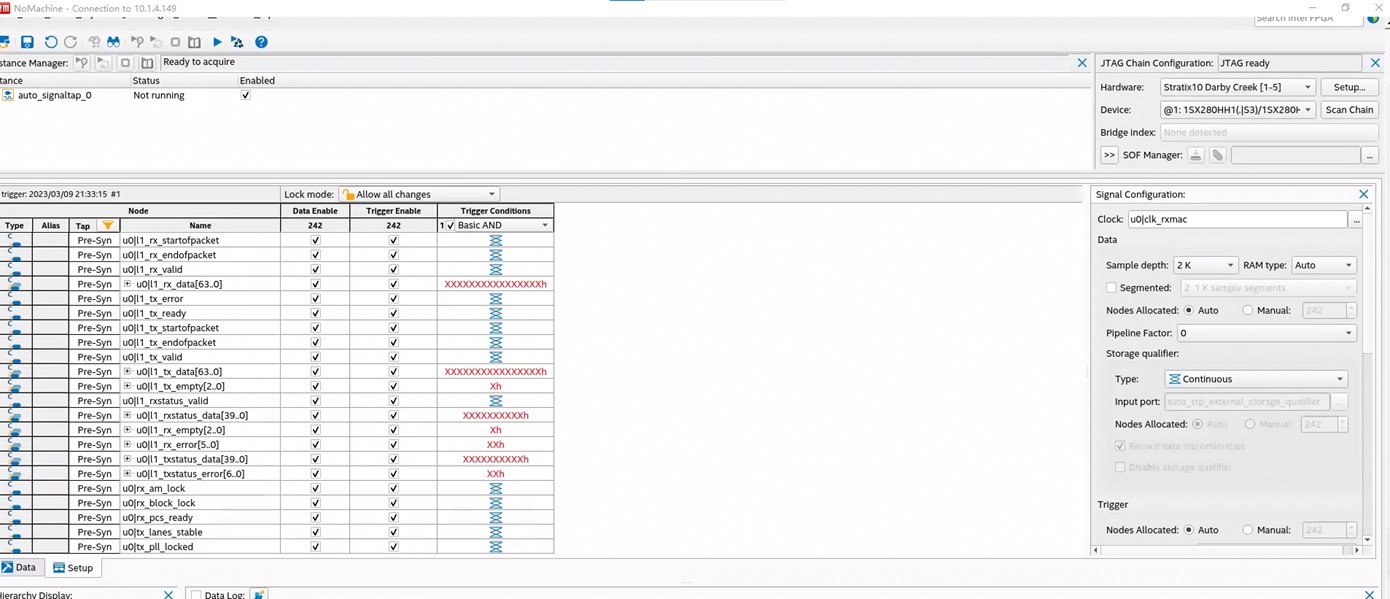

完成上述步骤后,新建 STP 文件。把相关需要观测的信号,添加到 STP 里,STP 采样时钟使用 clk_rxmac,添加要观测的信号,如下图 (图8) 所示:

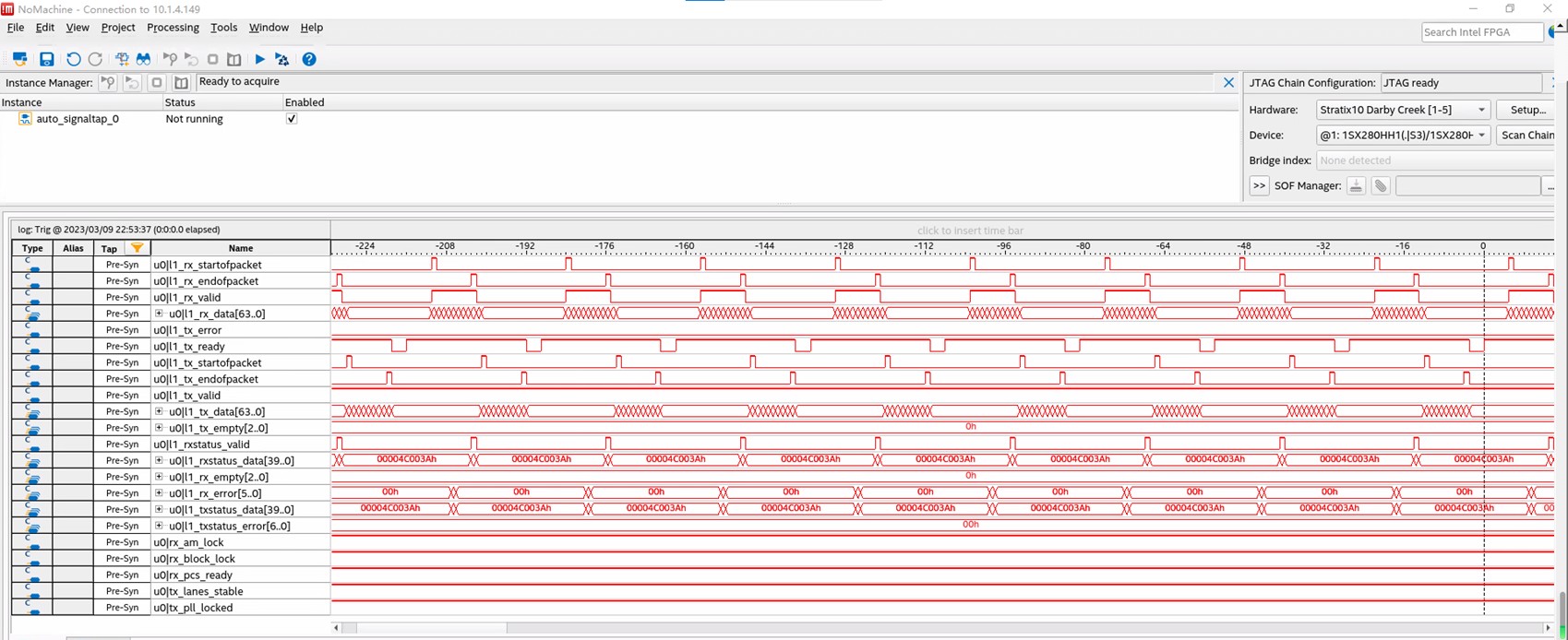

分配完管脚后,全编译工程。随后给板子上电,连接仿真器,烧写 sof 文件,使用 stp 抓取信号。下图 (图9) 为 stp 抓取信号示意图:

总结

本文通过配置 Altera 25G 以太网 IP 的 PMA 内部环回,实现了从新建工程、寄存器动态配置到硬件验证的完整流程。欲了解更多 Altera 相关方案或技术信息,可点击下方「联系我们」,提交您的需求,骏龙科技公司愿意为您提供更详细的技术解答。