# ADI solution for RF test instruments

Eric Cai Jay Huang

©2023 Analog Devices, Inc. All rights reserved.

1 //

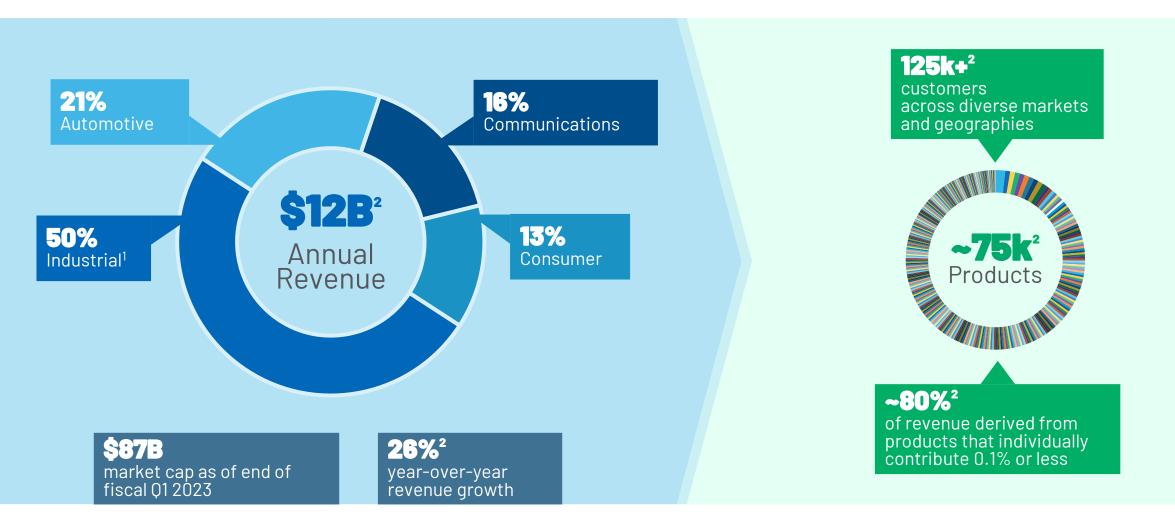

# Industry-Leading Financial Profile with **Scale**, **Scope**, and **Diversity**

Industrial automation, healthcare, aerospace, instrumentation and measurement, and energy management.

Information as of end of fiscal year 2022

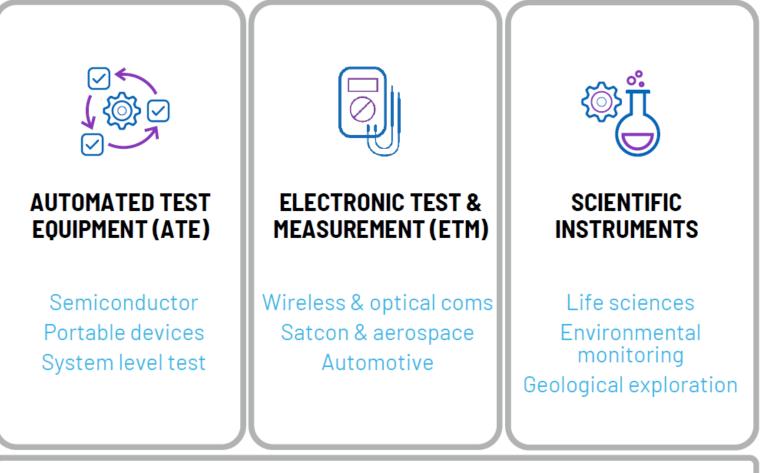

## Instrumentation segment snapshot

Market leader in high performance signal chains across precision, micromodule power, isolation, high-speed, & RF

**20,000+** customers

~30,000 SKUs

Strong Technology leverage Aligned with all secular mega-trends

#### SYSTEMS APPLICATIONS

Reference Designs, Signal Chains, Technical Support

#### **R&D and Field Deployed Measurement**

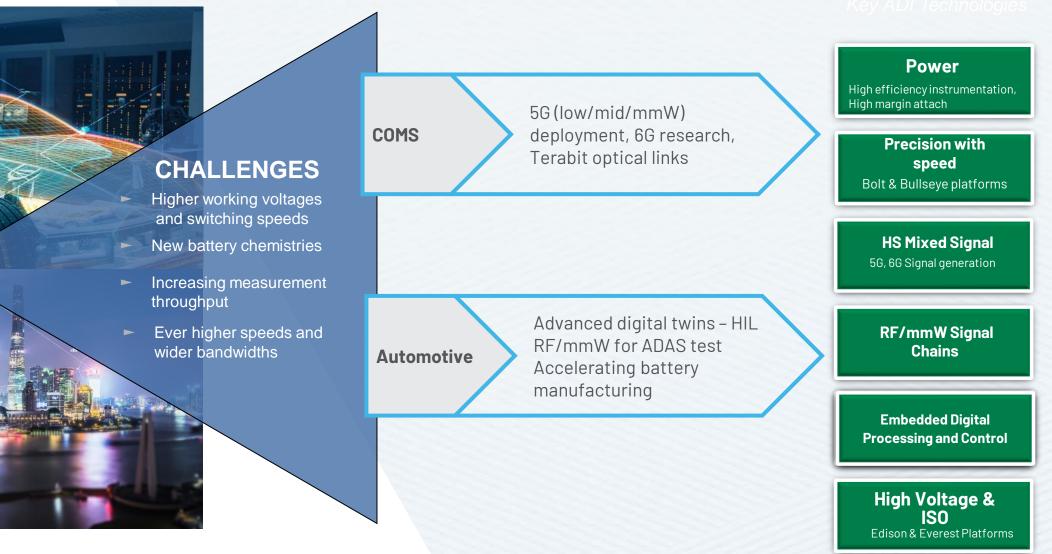

# Technology focus area

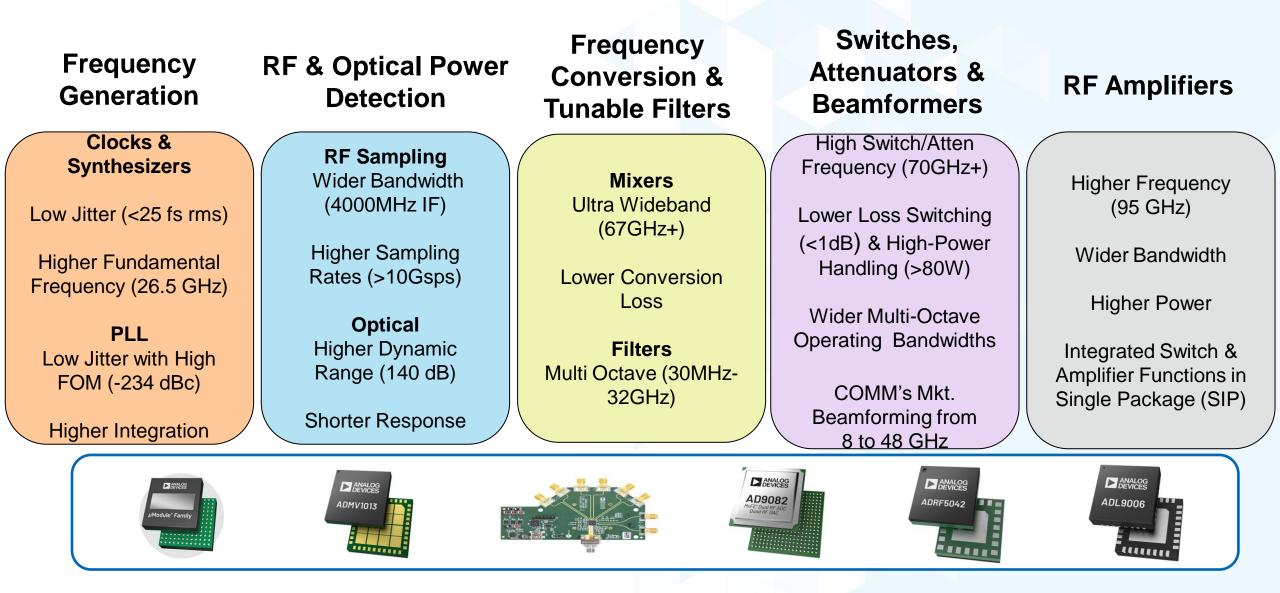

### ADI RF & Microwave Technology Supports Full Signal Chain Sell

### **RF** Architectures

| Туре                           | Configuration   | Benefits                                                                                                                                                                                                          | Challenges                                                                                                                                                                                         |

|--------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Heterodyne                     |                 | <ul> <li>Proven/Trusted</li> <li>High Performance</li> <li>Optimum Spurious</li> <li>High Dynamic Range</li> <li>EMI Immunity</li> </ul>                                                                          | <ul> <li>SWaP (Size, Weight, Power)</li> <li>Many Filters (some cannot be integrated)</li> <li>Image Rejection</li> </ul>                                                                          |

| Direct Conversion<br>(Zero IF) |                 | <ul> <li>Maximum A/D BW</li> <li>Simplest WB option</li> <li>Low Cost &amp; Power<br/>Consumption</li> <li>Less Filtering (mostly<br/>integrated on chip)</li> <li>LO Leakage</li> <li>Image Rejection</li> </ul> | <ul> <li>Image Rejection <ul> <li>IQ Imbalance</li> </ul> </li> <li>In-band IF harmonics</li> <li>LO Radiation (centered in band)</li> <li>EMI Immunity (IP2)</li> <li>DC and 1/f noise</li> </ul> |

| Direct Sampling                | Clock<br>RX A/D | <ul><li>No Mixing</li><li>Practical at L/S Band</li></ul>                                                                                                                                                         | <ul> <li>A/D Input BW</li> <li>Gain not distributed across<br/>Frequency</li> <li>Requires High Speed Sampling<br/>Data Converters</li> </ul>                                                      |

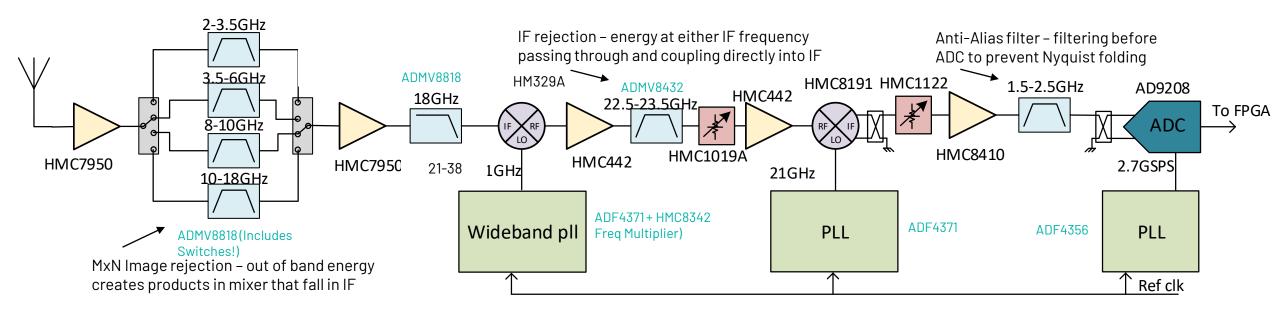

# Fill In Wideband RX Super Heterodyne Signal Chain

Populate rest of signal chain with frequency appropriate amplifiers, switches, filters, mixers, PLL/VCO

- Add any desired features such as digital step attenuators

- Can be used for gain leveling and Automatic Gain Control (AGC)

## **Precision Technology**

#### Where the Data is Born -

Source of data and bridge in connecting physical to digital world

#### **Standard Precision Products -**

Technology Leadership for 40+ years with the most advanced precision ADC and DAC cores as well as complete analog signal chains such as amplifiers, voltage references and signal chain umodules

#### ADI Internal IP Provider -

Develop break through converter cores that advance figure of merit as well as many system value adds such as low power, fast precision & high voltage operation.

# Industry Leading power Technologies

$\mu$ Modules

#### LTSpice & tools

nanoPower

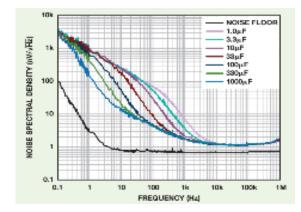

Ultralow Noise LDOs

Silent Switcher® 3

# ADI products and solutions in RF instruments

# **Communications Test Application Examples**

#### Wireless Communications Test

- ► Highly integrated for 5G, WiFi Test

- 5G Signaling Test; 5G call with DUT

- ► RF characteristics, protocol compliance

#### **High Speed Benchtop Equipment**

- Spectrum Analyzers, VNAs

- Signal Generators

- Channel Emulators

- RF to mmWave measurements

#### **Portable Testers**

- Handheld Spectrum Analyzers, VNAs

- Field Deployed

- Low Power dissipation, small footprint

#### **Wired Communications Test**

- Time domain, High Speed Data (PCIe, GbE)

- Datacenters, High Speed Computing

- Oscilloscopes, Digitizers, Bit Error Rate Testers

OTDR & Protocol Analyzers

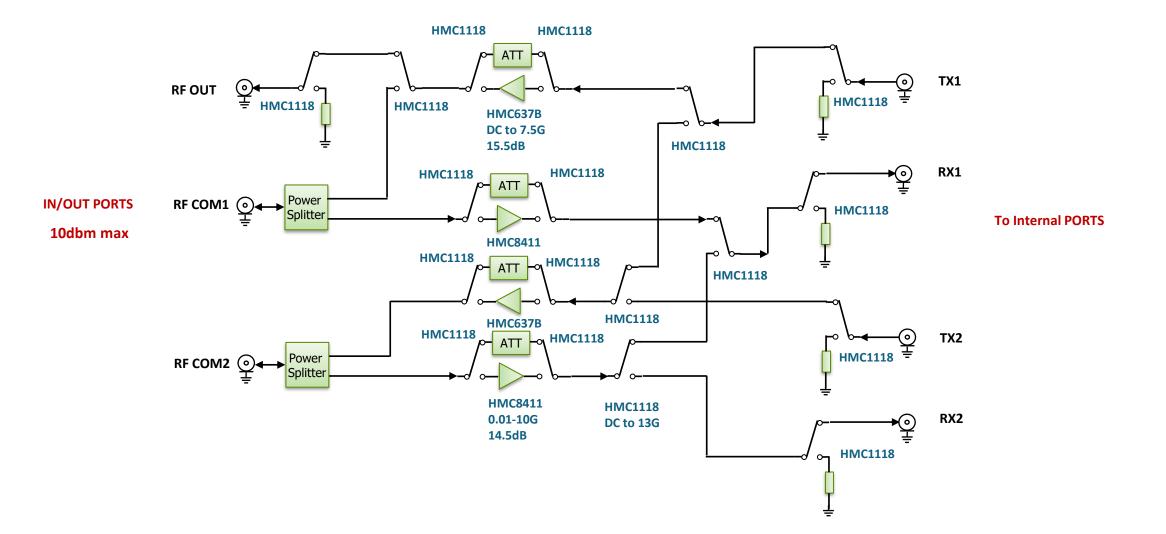

### Universal Wireless Tester --- Front End Signal Path

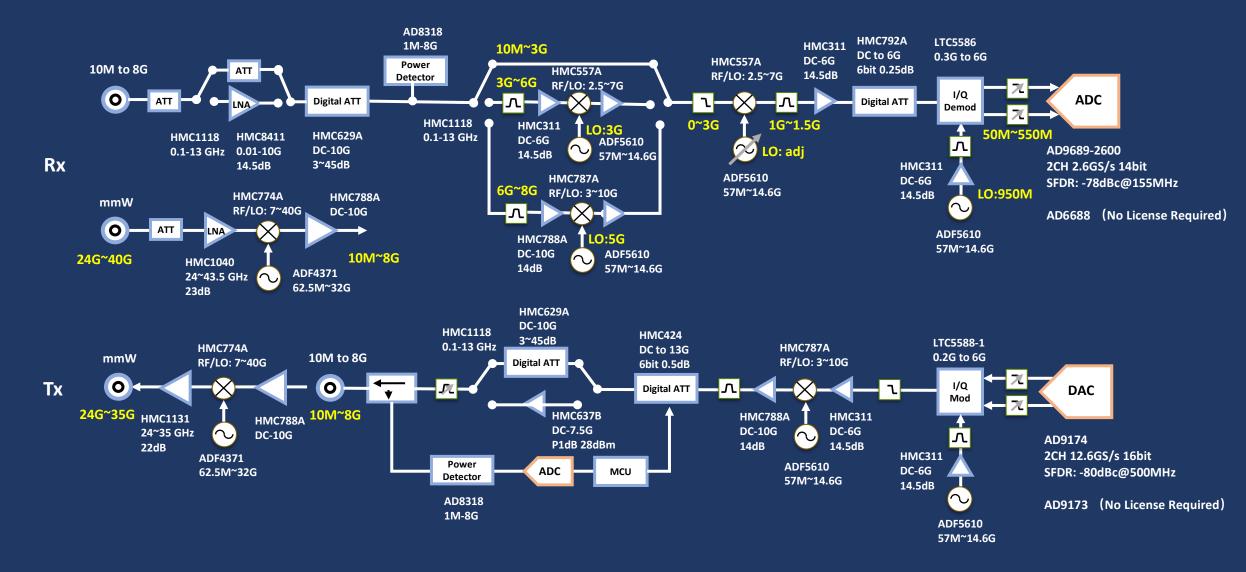

#### 5G Universal Wireless Tester --- ADI 500M BW Sub 8GHz / mmW Signal Chain

#### **Some Strengths of both techniques**

#### PLL

- Can achieve GHz frequencies

- Fractional-N design achieves good frequency resolution

- Can be very low power

- Does not require reconstruction filter

- Reference frequency lower than output frequencies

#### DDS

- Extremely high frequency resolution

- Agile no settling time or overshoot for frequency shifts

- Can be phase and amplitude modulated

- Multiple DDSs can be synchronized

- Inherently digitally controlled

#### **Some Limitations of both techniques**

#### PLL

- VCO is a critical component

- Integer-N PLL design limits frequency resolution

- Loop settling characteristics affect settling time and overshoot during frequency shifts

- Loop multiplication factor increases phase noise of RF

#### DDS

- Requires DDS clock more than 2X desired output frequency

- Requires external reconstruction filter

- Higher frequency operation requires more power

- Output frequency limited to less than half of DDS clock frequency

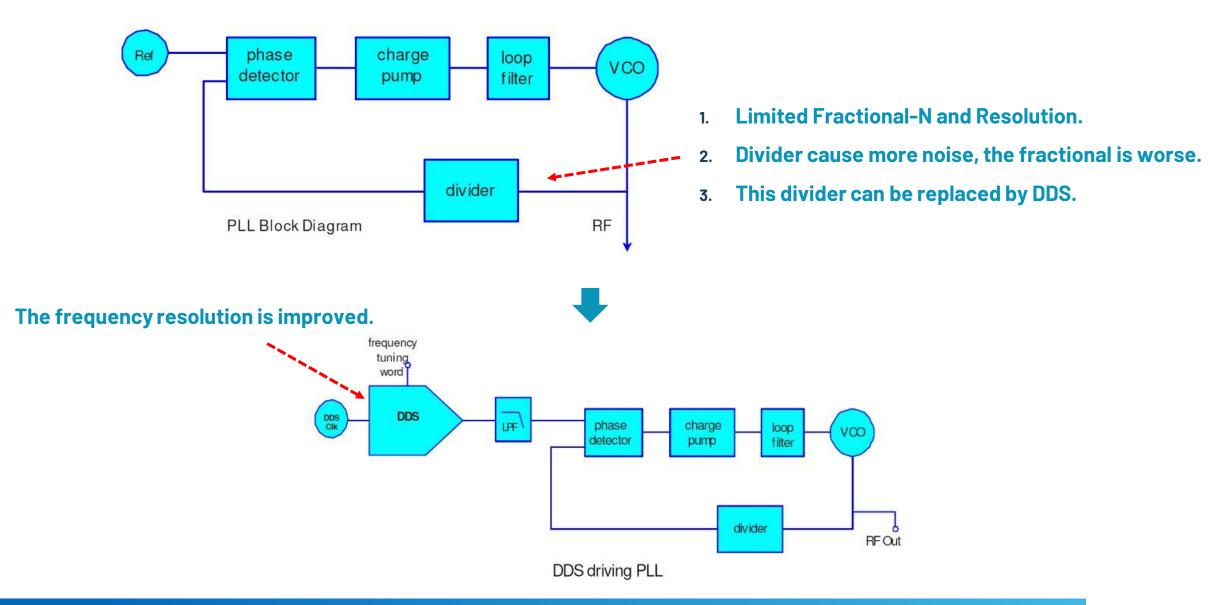

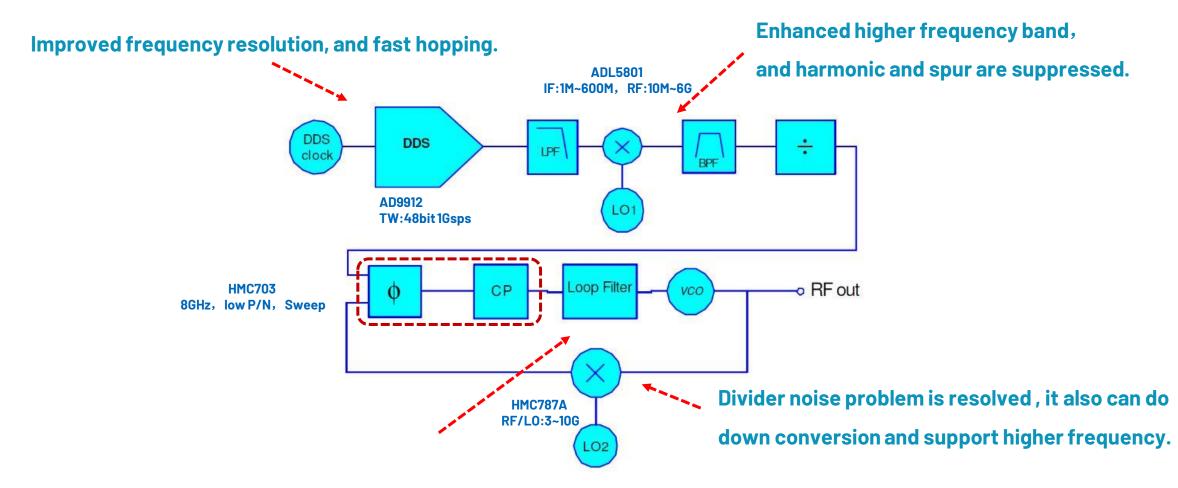

#### **Combining Strengths – Overcoming Limitations**

- PLL and DDS techniques can be combined to achieve what neither one alone can manage

- Combining a DDS with a PLL in an RF synthesizer design allows the frequency resolution and controllability of the DDS, and the frequency range of the PLL

- In some architectures the DDS allows for a lower frequency multiplication factor, enhancing phase noise performance

- The PLL can reduce DDS spurs

- Together, PLL and DDS enable high performance RF synthesizer designs

# Frequency Synthesizer: with DDS added

- 1. Lock time is based on loop bandwidth and VCO calibration speed.

- 2. It can save lock time if use manual VCO band config or use a stand alone VCO.

# VNA solution

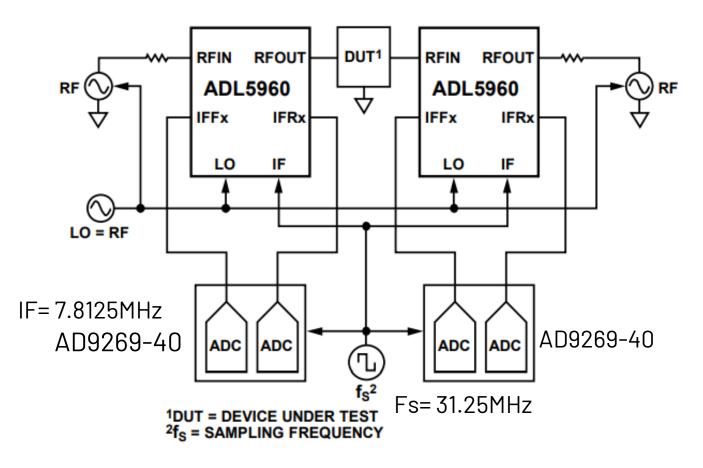

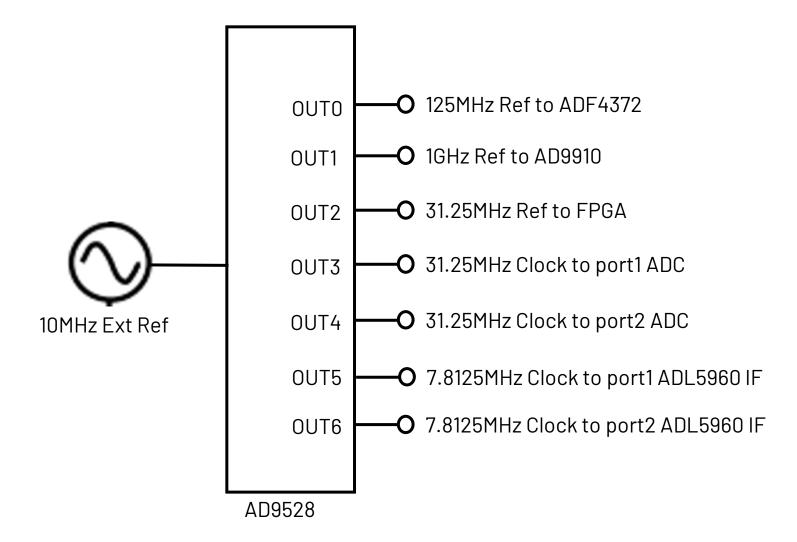

# 8-Port VNA (Vector Network Analyzer)

- Wide Bandwidth and Small Solution Size

- 10MHz to 20GHz

- 7in x 6.5in board

- Fully functional for turnkey evaluation

- Plugs into Xlinx ZCU102 development board

- Complete software, firmware and GUI

- Programmable IF Filters and Amplifiers

- LO Frequency Multiplier and Divider

- 6GHz frequency synthesizer as local oscillator to measure 20GHz

- Offset Frequency Mixer and Divier

- RF and LO interfaces requires only a single high frequency source

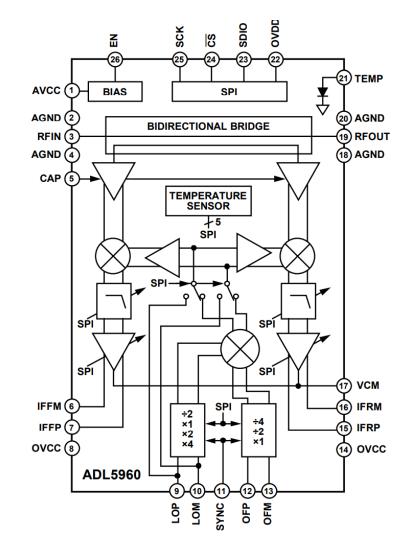

# ADL5960 and ADL5960 based VNA block diagram

\*: ADL5960 offset mode and internal LO doubler will be used.

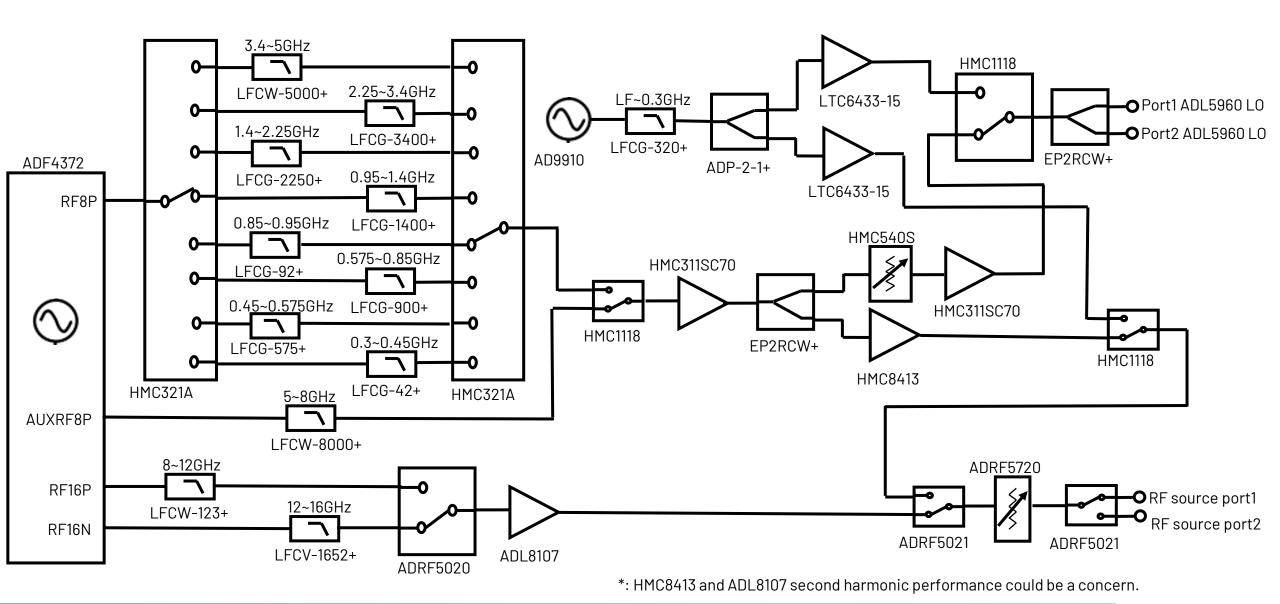

# RF source implementation

Need to measure on Eva board.

# Thanks