如何使用 Signal Probe 进行 FPGA 调试

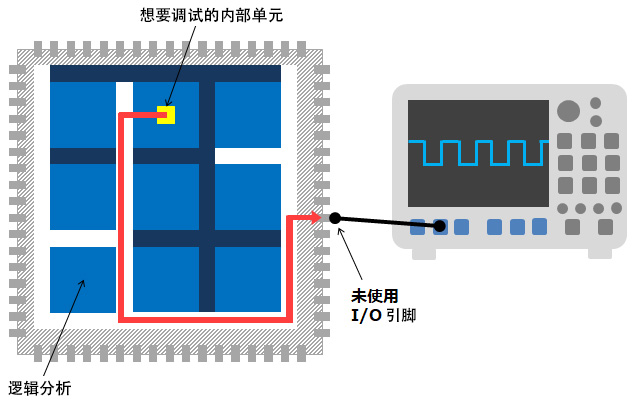

英特尔 FPGA 设计软件 Quartus® Prime 包括多种调试功能,其中之一是 Signal Probe,下图 (图1) 为它的示意图。Signal Probe 是一个有效的调试工具,将 FPGA 内部需要探测的信号连接到未使用的 I/O 管脚输出,即可使用外部设备 (如示波器或逻辑分析仪) 观察到该信号的情况。更有效的是,在保留先前编译结果的同时,Signal Probe 无需改变原有设计,而是使用冗余的引脚作为输出,实现快速地设计调试。

Signal Probe 特点

- 无需编辑设计,即可将内部信号布线到调试端口

- 需要足够的 I/O 引脚进行调试

- 占用设备内部资源少

- 使用外部测试设备

- 无需 JTAG 连接

- 可免费使用

下表为 Signal Probe 和 Signal Tap 逻辑分析仪的比较:(* 烧录 sof/pof 数据需要 JTAG 连接)

| 要求 | Signal Probe | Signal Tap 逻辑分析仪 |

| 需要外部设备 | 〇 | X |

| 需要 JTAG 连接 | X | 〇 |

| 足够的 I/O 引脚 | 〇 | X |

| 未使用的内部逻辑和所需的内存 | X | 〇 |

| 高级触发功能 | X | 〇 |

Signal Probe 与 Quartus Prime

英特尔 FPGA 设计软件 Quartus® Prim 有多个版本,每个版本提供不同的功能和特性。以下是一些常见的 Quartus 版本:

- Quartus Prime Pro Edition (专业版)

- Quartus Prime Standard Edition (标准版)

- Quartus Prime Lite Edition (精简版)

Signal Probe 是 Quartus Prime 支持的一项功能。Signal Probe 适用于 Quartus Prime 支持的所有系列,但对于 Arria® 10,请使用 Quartus Prime Pro Edition (不支持标准版),Signal Probe 也支持 CPLD 系列。

| Quartus Prime | 运行细节 | 处理方法 | 编译 |

| Pro Edition |

|

用脚本设置 | Rapid Recompile |

|

Standard Edition Lite Edition |

Signal Probe专用 使用 GUI配置 |

Signal Probe Compilation (※ECO编译) |

※ECO:Engineering Change Order

Quartus Prime Pro Edition 操作方法

在专业版中,使用脚本配置以下操作:

- 为 Signal Probe 创建引脚

- 将需要探测的内部信号分配给 Signal Probe 引脚

在下面的示例中,Signal Probe 的引脚名称为 sp_moni。假设项目设计已经编译完成,开始以下步骤:

① 选择“文件”菜单 > 打开以文本形式打开项目的 .qsf 文件。

② 在 .qsf 文件中添加并保存以下命令,以保留 Signal Probe 引脚。<pin_name> 指定为 Signal Probe 创建的引脚名称:set_global_assignment -name CREATE_SIGNALPROBE_PIN <pin_name>,例如:set_global_assignment -name CREATE_SIGNALPROBE_PIN sp_moni。

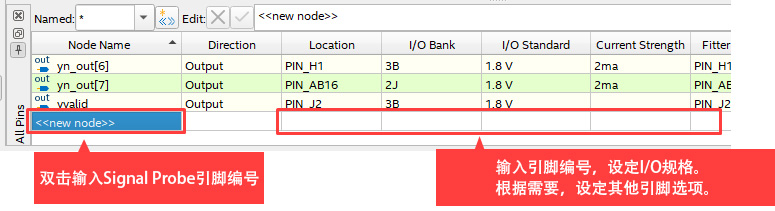

③ 在 Pin Planner 中,将步骤②中为 Signal Probe 创建的引脚名称输入到 Node Name 字段中的 <<new node>>,然后指定引脚位置、I/O 标准等。

④ 运行编译。

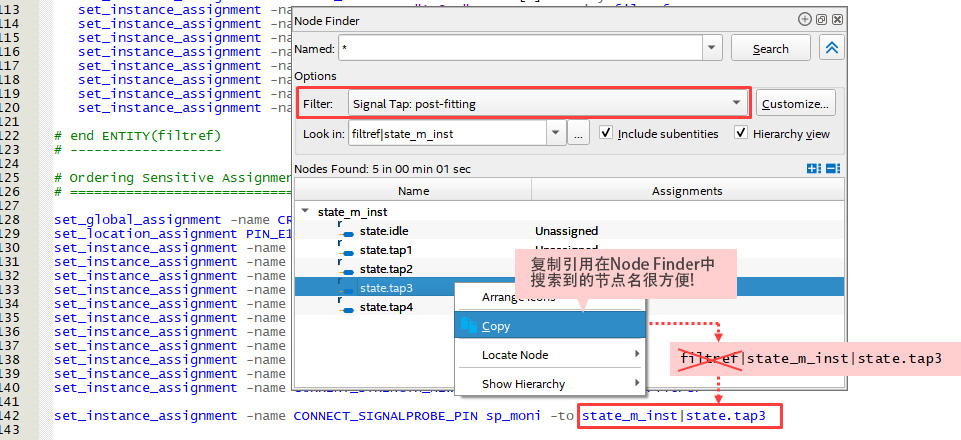

⑤ 将以下命令添加并保存到 .qsf 文件中,并将内部节点分配给为 Signal Probe 创建的引脚:set_instance_assignment -name CONNECT_SIGNALPROBE_PIN <pin_name> -to <node_name>。其中,<pin_name> 指定为信号探针创建的引脚的名称,<node_name> 指定要监视的内部节点。内部节点必须用分层路径来描述,因此在“View”菜单 > “Node Finder”中,将“Filter”设置为“Signal Tap: post-fitting”,并使用“Search”按钮找到的节点名称。

接下来复制所需的节点名称并将其粘贴到 <node_name> 部件中。在这个过程中,请删除不需要的顶层实体名称:set_instance_assignment -name CONNECT_SIGNALPROBE_PIN sp_moni -to state_m_inst|state.tap3

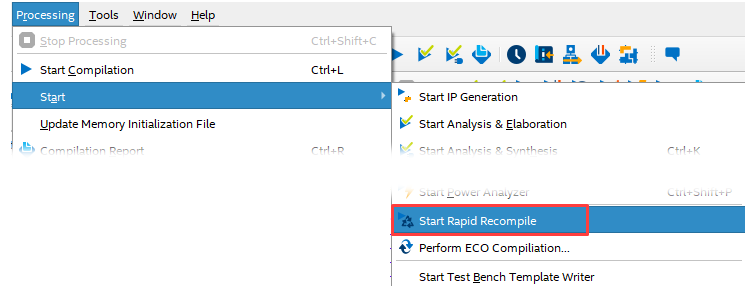

⑥ 重新编译设计。在这种情况下,如果没有设计更改,只需添加一个 Signal Probe 引脚,则不需要通常的完全编译,建议使用 Rapid Recompile,步骤如下:Processing 菜单 > Start > Start Rapid Recompile。

如果为了在 Pro Edition 中执行快速重新编译,必须要在 Fitter 中生成快照。但为了让 Fitter 生成快照,则必须在启用以下选项的情况下执行完整编译:Enable Intermediate Fitter Snapshots = On (Assignments 菜单 > Settings > Compiler Settings)

需要注意,在 ver.18.0 Pro Edition 中,此选项不存在。但在 Rapid Recompile 运行过程中,如果出现"Rapid Recompile database does not exite."或没有收到"Rapid Recompile could not locate a design database from a previous compilation on disk.",则不需要。

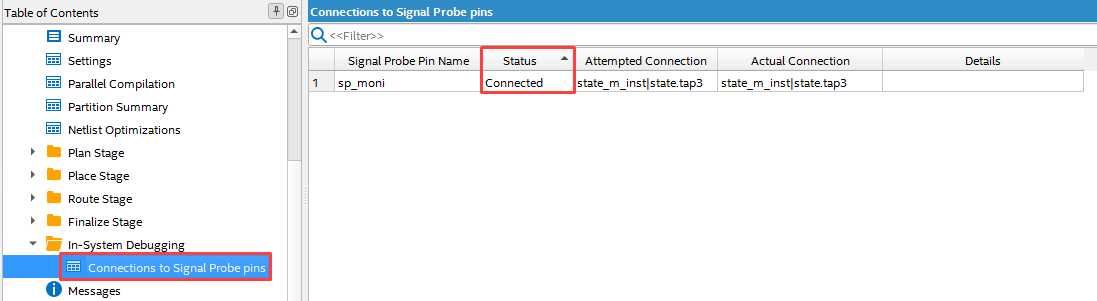

⑦ 在“编译报告” (“Processing”菜单 > Compilation Report) 中,单击 Fitter 文件夹 > In-System Debugging 文件夹 > Connections to Signal Probe pins,检查“Status”列中的符号,确认内部信号是否已路由到 Signal Probe 引脚。

| Status | 说明 |

| Connected | 路由成功。 |

| Unconnected |

路由不成功。原因可能有: |

⑧ 将文件写入设备后,使用外部测量仪器 (如逻辑分析仪、示波器等) 观察带有 Signal Probe 的引脚。

Quartus Prime Standard/Lite Edition 操作方法

在标准版和精简版中,使用 Signal Probe 专用 GUI 配置以下操作:

- 为 Signal Probe 创建引脚

- 将要监控的内部信号分配给 Signal Probe 引脚

在下面的示例中,Signal Probe 的引脚名称为 sp_moni,假设项目设计已经编译完成:

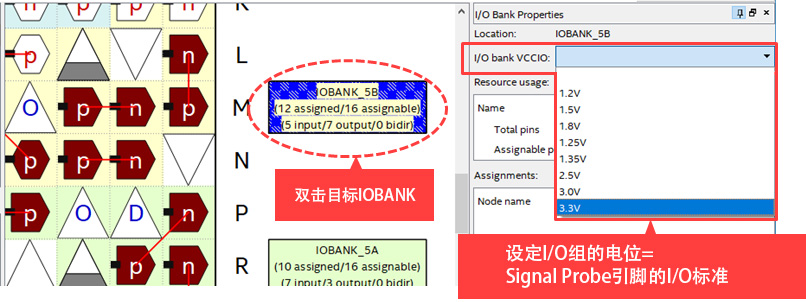

① 预先设置 Signal Probe 引脚的 I/O 标准。请注意:Signal Probe 引脚的 I/O 标准由要放置的引脚号所属的 I/O 组的 VCCIO 电位设置决定,取决于默认 I/O 标准的潜在设置值。如果没有单独设置 I/O 组的 VCCIO 电位,请在 Device and Pin Options 的 Voltage 中进行设置 (Assignments 菜单 > Device)。因此请预先设置分配了 Signal Probe 引脚的引脚编号所属 I/O Bank 的电位。如下图所示,启动 Assignments 菜单的 Pin Planner,然后双击所需的 IOBANK_XX。在出现的 I/O Bank Properties 窗口中,设置 I/O Bank VCCIO。

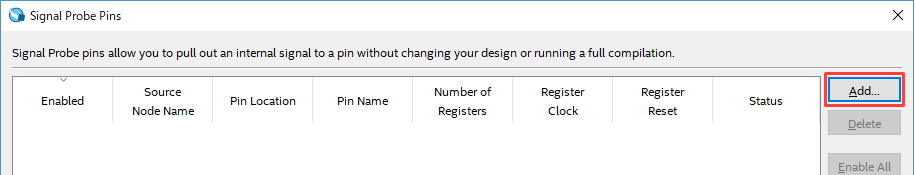

② 启动 Tools 菜单 > Signal Probe 引脚。单击“Add”按钮时,将出现“Add Signal Probe Pin”对话框。

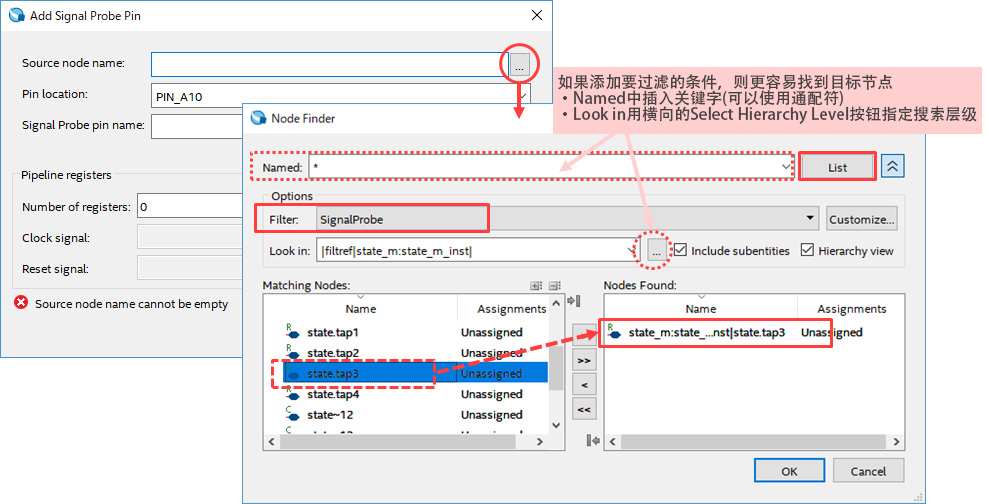

③ 在“Add Signal Probe Pin”对话框中,单击“Source node name”右侧的浏览按钮以启动“Source node name”。将 Filter 设置为“SignalProbe”,然后单击“List”按钮。在监测到的节点中,从“List”字段到“Nodes Found”字段中选择要监视的节点。

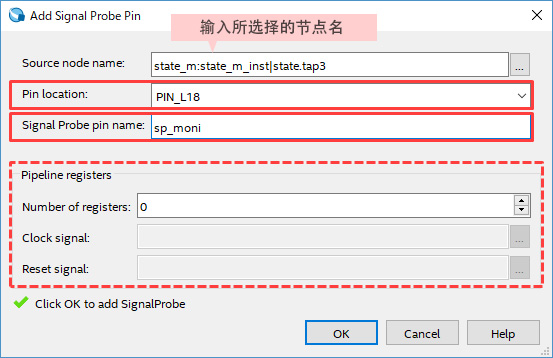

④ 在“Add Signal Probe Pin”对话框中设置其他项目。如果要在设置后更改内容,请双击每个项目并进行编辑。

| Pin location | 选择要为 Signal Probe 分配引脚的引脚编号 (该列表仅显示未使用的用户 I/O 引脚编号) |

| Signal Probe pin name | 输入 Signal Probe 的引脚名称 (在此示例中,输入 sp_moni) |

| Pipeline registers | 如果要在 Signal Probe 输出的信号中插入寄存器,请设置以下内容: ・插入寄存器数 ・控制寄存器的时钟信号 ・控制寄存器的复位信号 |

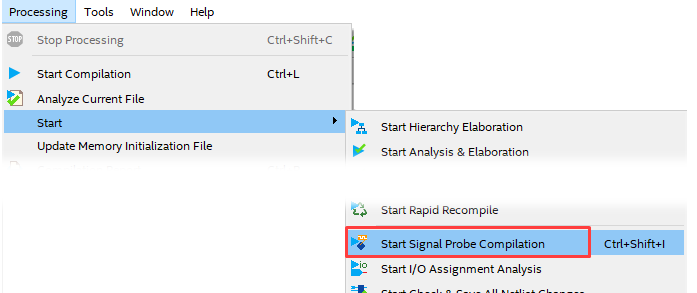

⑤ 运行 Signal Probe Compilation:Processing 菜单 > Start > Start Signal Probe Compilation,ECO (Engineering Change Order) 执行编译。

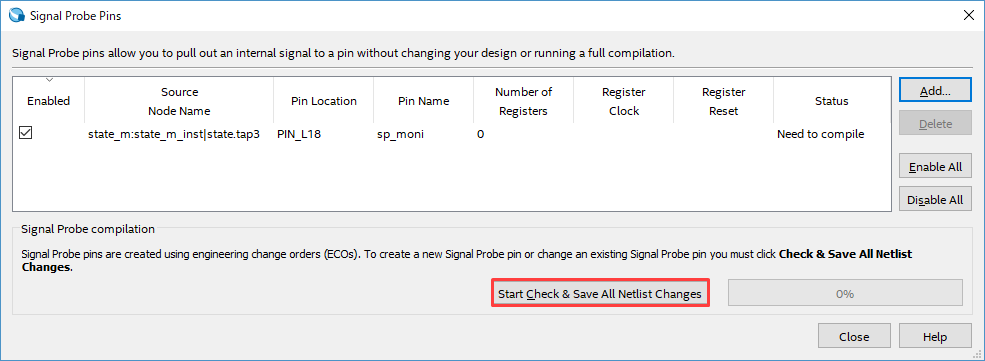

如果 Start Signal Probe Compilation 处于非活动状态且无法选择,请启动 Signal Probe Pin > Tools 菜单,然后单击对话框右下角的“Start Check & Save All Netlist Changes”按钮。确认“ECO Fitting was success”消息后,Signal Probe Compile 完成。

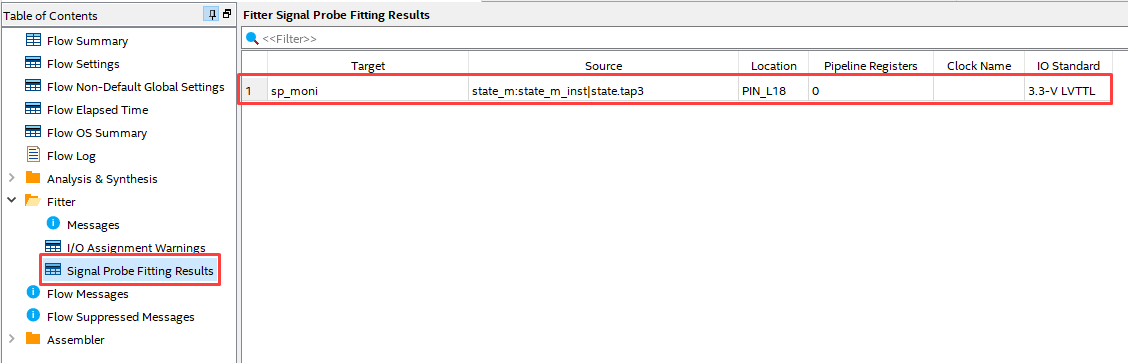

⑥ 在编译报告 (Processing 菜单 > Compilation Report) 中,单击 Fitter 文件夹 > Signal Probe Fitting Results,验证内部信号是否已成功路由到 Signal Probe 引脚。

⑦ 将文件写入设备后,使用外部测量仪器 (如逻辑分析仪、示波器等) 观察带有 Signal Probe 的引脚。

Signal Probe 编译错误解决方法

如果执行 Signal Probe Compilation 时出现以下错误,则 Signal Probe 引脚的 I/O 标准可能未正确设置 (仅限标准版和精简版)。

ID:169026

Pin <name> with I/O standard assignment <name> is incompatible with I/O bank <name>. I/O standard <name>, has a VCCIO requirement of <number>, which incompatible with the I/O bank's VCCIO setting or with other output or bidirectional pins in the I/O bank using a VCCIO requirement of <number>. Assign output and bidirectional pins with different VCCIO requirements to different I/O banks, or change the I/O standard assignment for the specified pin to a compatible I/O standard. The Intel FPGA Knowledge Database contains many articles with specific details on how to resolve this error. Visit the Knowledge Database at https://www.altera.com/support/support-resources/knowledge-base/search.html and search for this specific error message number.

Signal Probe 编译期间出现错误可能是由于在 Signal Probe 引脚上设置的 I/O 标准电位与 Signal Probe 所属 I/O Bank 的 VCCIO 电位不匹配。为避免这种情况,请执行以下操作:

- 在 Signal Probe Pins 中,删除相应的配置 (Delete)

- 如步骤①所示,正确设置 I/O bank 的电位

- 在 Signal Probe Pins 中再次设置引脚

- 执行开始检查并保存 Signal Probe Pins 中的 Netlist Changes

总结

本文主要介绍了英特尔 FPGA 设计软件 Quartus® Prim 中 Signal Probe 的功能特点,以及三种不同 Quartus Prime 版本下,Signal Probe 的运行步骤和注意事项。欲了解更多英特尔相关方案或技术信息,可点击下方「联系我们」,提交您的需求,骏龙科技公司愿意为您提供更详细的技术解答。