基于Cyclone10LP器件,如何实现串行通信的数据恢复?

对于非源同步的低速串行数据通信场景,会存在通信对端的时钟频率相对有偏差的情况,导致数据接收端不能正确的采样;这时候利用Altera中高端器件的高速收发器或者LVDS serdes中的SOFT-CDR及DPA功能便能解决此问题;但是对于类似Cyclone IV或Cyclone 10LP等中低端器件,既没有高速收发器,LVDSserdes也不具备SOFT-CDR及DPA功能,所以只能通过我们自行设计逻辑来实现串行数据的恢复。

本设计的技巧是利用接收端的参考时钟,通过对其相移0°和相移90°的两个时钟的上下沿,对接收的数据做8倍过采样,再通过逻辑来判断如何选取稳定时钟域,并以该时钟域采样的数据作为可靠数据。

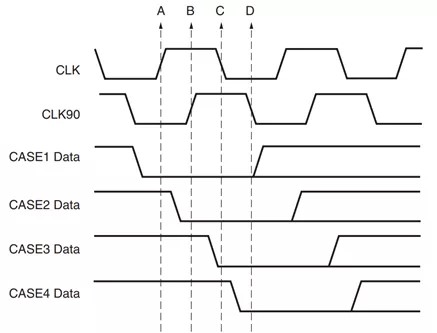

图 1

如图1所示,第一个触发器由被描述为时域A的CLK上升沿采样,第二个触发器由时域B即CLK90的上升沿采样,第三个触发器由时域C即CLK下降沿采样,第四个触发器由时域D即CLK90的下降沿采样。

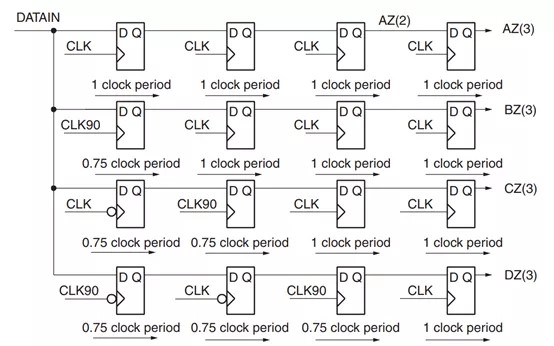

当然,为了消除亚稳态,光使用一级采样是肯定不够的,需要对这四个触发器分别做四级采样来消除亚稳态,如图2所示:

图 2

我们按照图2进行触发器逐级采样后,命名第三级触发器分别为AZ(2),BZ(2),CZ(2),DZ(2);命名第四级触发器分别为AZ(3),BZ(3),CZ(3),DZ(3)。

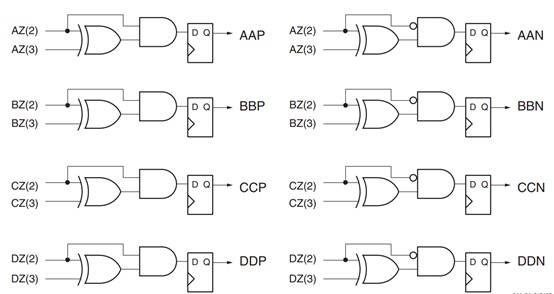

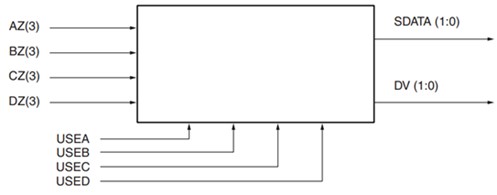

数据经过四个时钟域分别四级采样之后,再做一个组合逻辑,如图3:

图 3

按照图3依次做异或、与/与非逻辑后,经过触发器依次得到数据AAP,AAN,BBP,BBN,CCP,CCN,DDP,DDN;

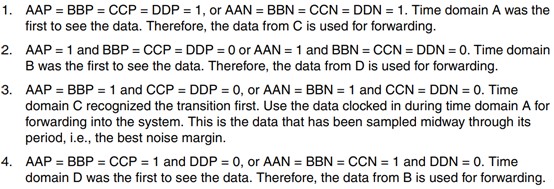

之后就需要进行可靠时钟域的判决,即挑选采样数据最稳定的时钟域:

在实际情况中,我们可能会遇到:例如数据发送端时钟频率是401MHz,而本地采样时钟频率是400MHz,或相反发送端是400MHz,而本地是401MHz的情况;通过仿真发现在此情形下,判决的结果会进行周期性的变化,即一段时间后判决为稳定的时钟域可能从D变为A,但这并没有关系,按照其判决为最可靠的时钟域去采样数据,最后得到的实际数据一定是正确的。

由于可靠时钟域的判决结果会进行变化,我们需要设计一小段逻辑来进行数据筛选,如图4:

图 4

本设计的主要目的就是为了找到那个能稳定采样数据的最可靠时钟域,即使这个时钟域可能因通信对端时钟频偏差而动态变化,最后基于这个时钟域的采样数据都是稳定可靠的。目前我在某工业客户的硬件基础上,基于10CL010YU256C8G和10CL016YU256C8G验证数据串行通信,长时间挂机测试伪随机码通信,其误码率为0;该客户相关产品已经量产。当然,为了更加可靠的通信质量,我们在实际产品中也会加入8B10B编解码模块。