基于 Altera Nios II Eclipse 环境的 DP 软件工程编译与屏幕点亮指南

本文主要介绍在 Altera Arria 10 器件上使用 Altera Nios II Eclipse 环境完成 DP (DisplayPort) 链路训练软件代码编译,并且通过 Nios II command 进行 elf 下载及屏幕点亮的完整操作流程和技术要点。

一、Altera Nios II 简介

Nios II 是 Altera 推出的 32 位 RISC 嵌入式处理器软核,作为 FPGA 可编程逻辑器件的配套处理器解决方案。该处理器采用可配置架构设计,支持从低成本 (Nios II/e) 到高性能 (Nios II/f) 的多级配置方案,能够通过 QSYS/Avalon 总线与 FPGA 逻辑实现深度集成。

Nios II 处理器提供完整的软件开发工具链,配套的 Nios II Eclipse 开发环境基于 Eclipse 框架构建,集成了工程管理、代码编辑与调试、BSP (Board Support Package) 配置以及硬件/软件协同设计等核心功能,同时支持 200 余种 IP 核,包括 DMA 控制器、定时器模块和各种通信接口等外设组件,为 FPGA 嵌入式系统开发提供完整的软硬件解决方案。

二、开发环境准备及工程导入

(一) 开发环境准备

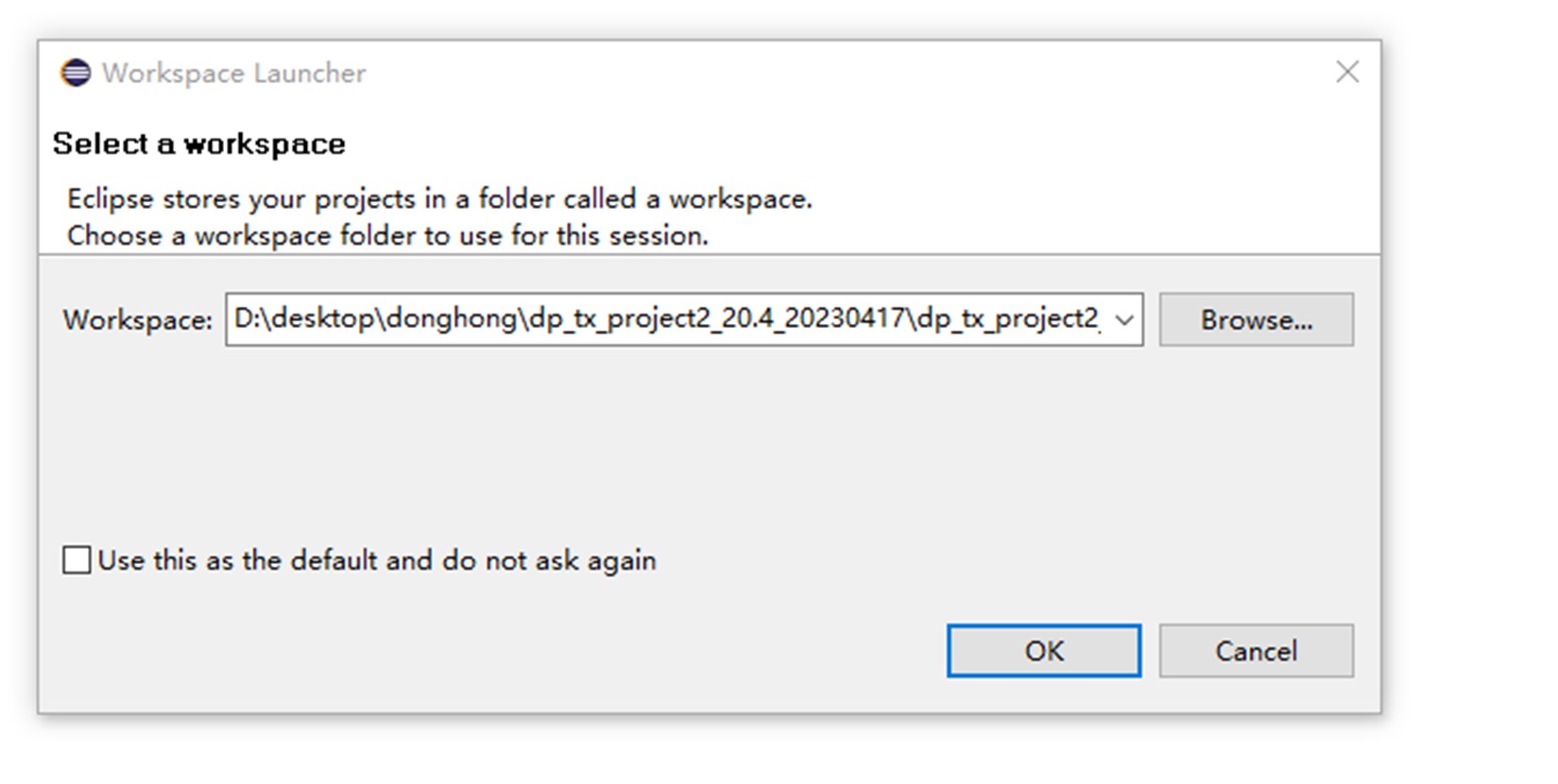

打开 Nios II Eclips,将工作区间定位到工程目录下 software 文件夹,如下图 (图1) 所示:

(二) 工程导入

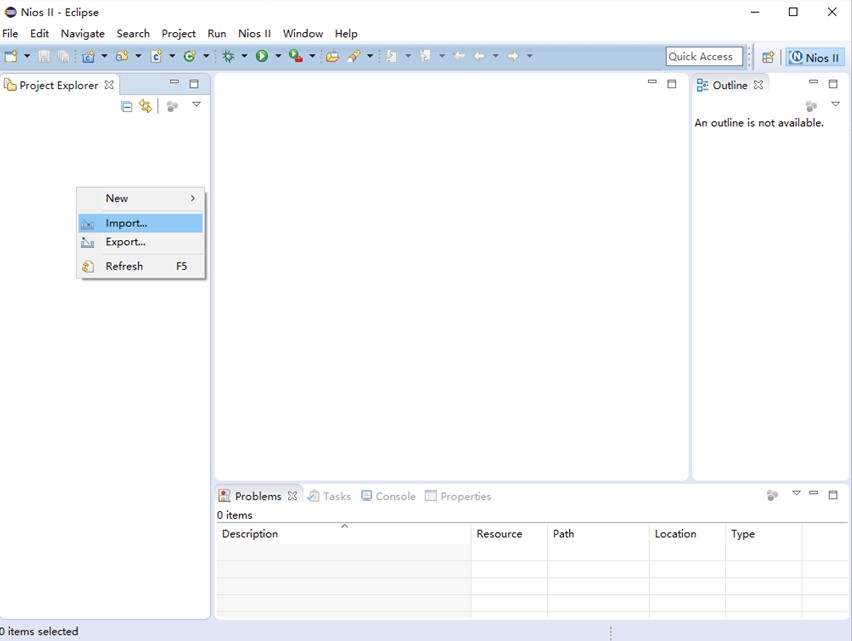

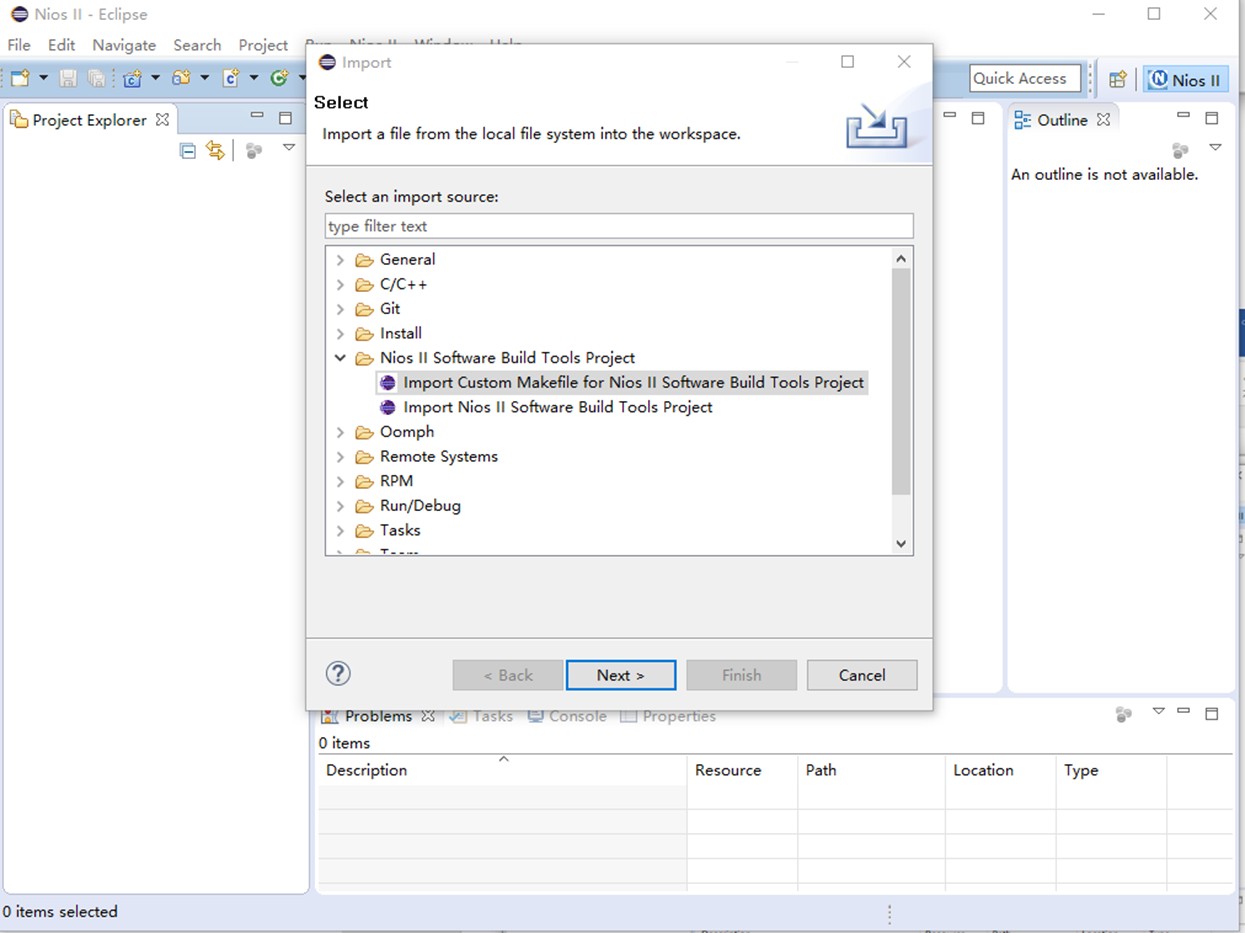

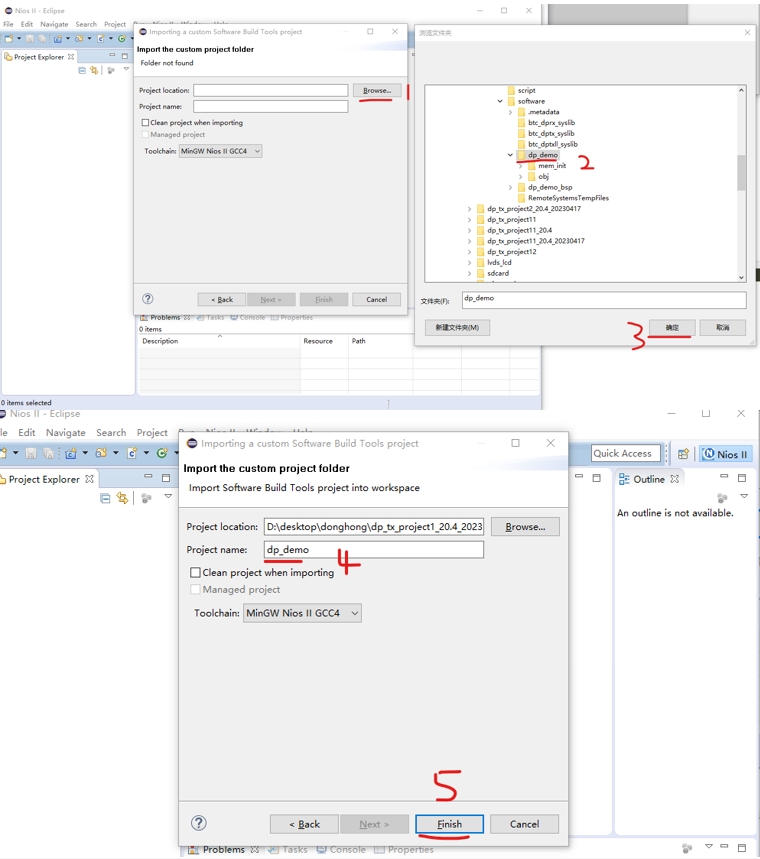

右键点击“Import”功能 (图2),选择“Import Custom Makefile for Nios II Software Bulid Tools Project”(图3):

接下来可按照如下图 (图4) 所示步骤 1-5,把 software 文件夹下的 dp_demo 工程添加进来:

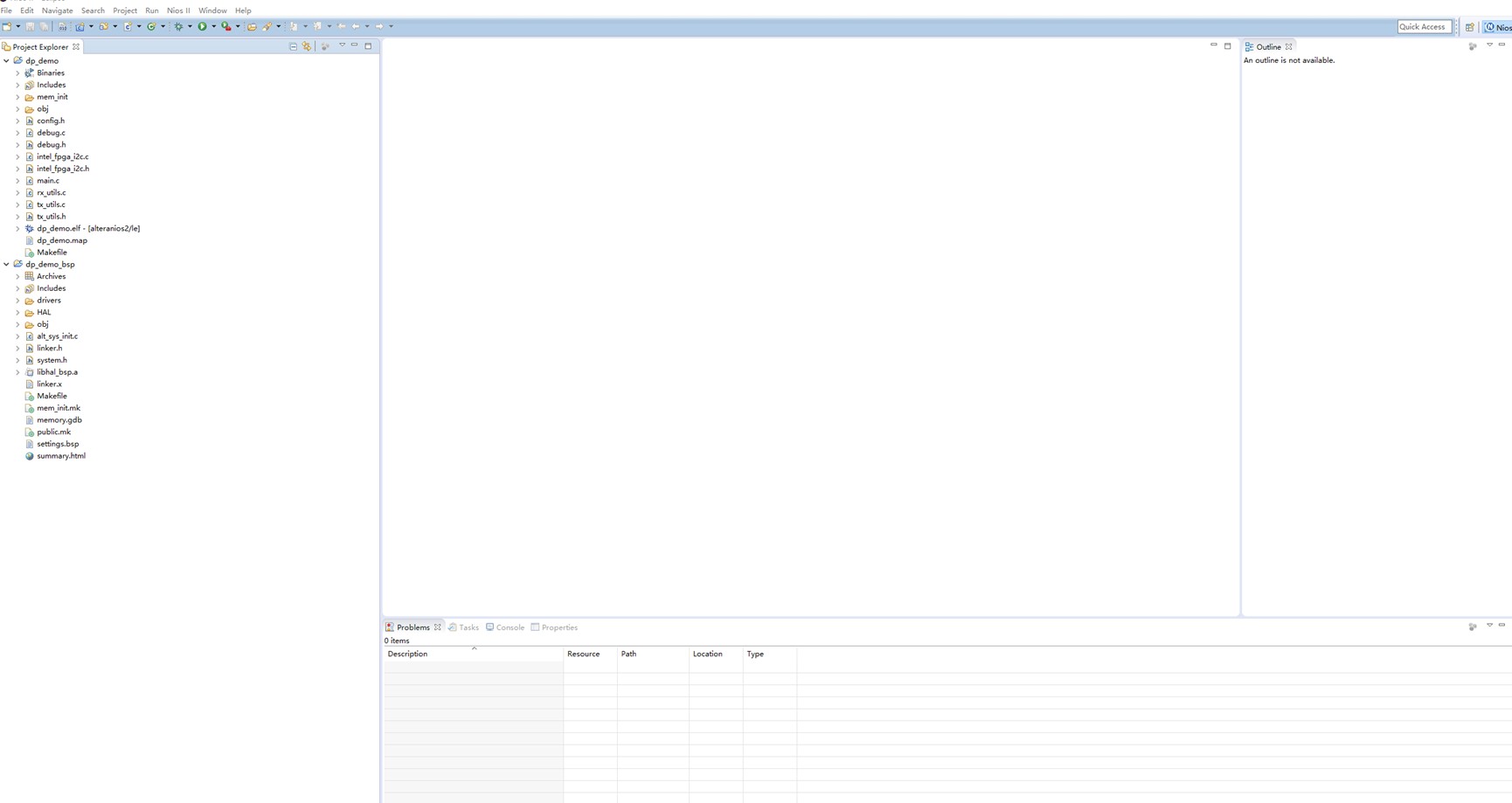

添加完成后,导入的 dp_demo 工程会显示在左侧“Project Explorer”中。按照同样步骤添加 dp_demo_bsp 工程,dp_demo 和 dp_demo_bsp 添加完成如下图 (图5),左侧“Project Explorer”工程列表中应显示显示 dp_demo 和 dp_demo_bsp 两个项目。

三、工程编译与硬件配置

右键点击工程,选择“build project”进行编译。build 之前,elf 文件为旧的时间,build 之后,elf 为新的时间。如果时间没有更新,可以先把老的备份删除,再进行 build。也可以通过 Nios II Eclips 开发工具根据自己项目的需求进行修改代码,然后再进行 build。

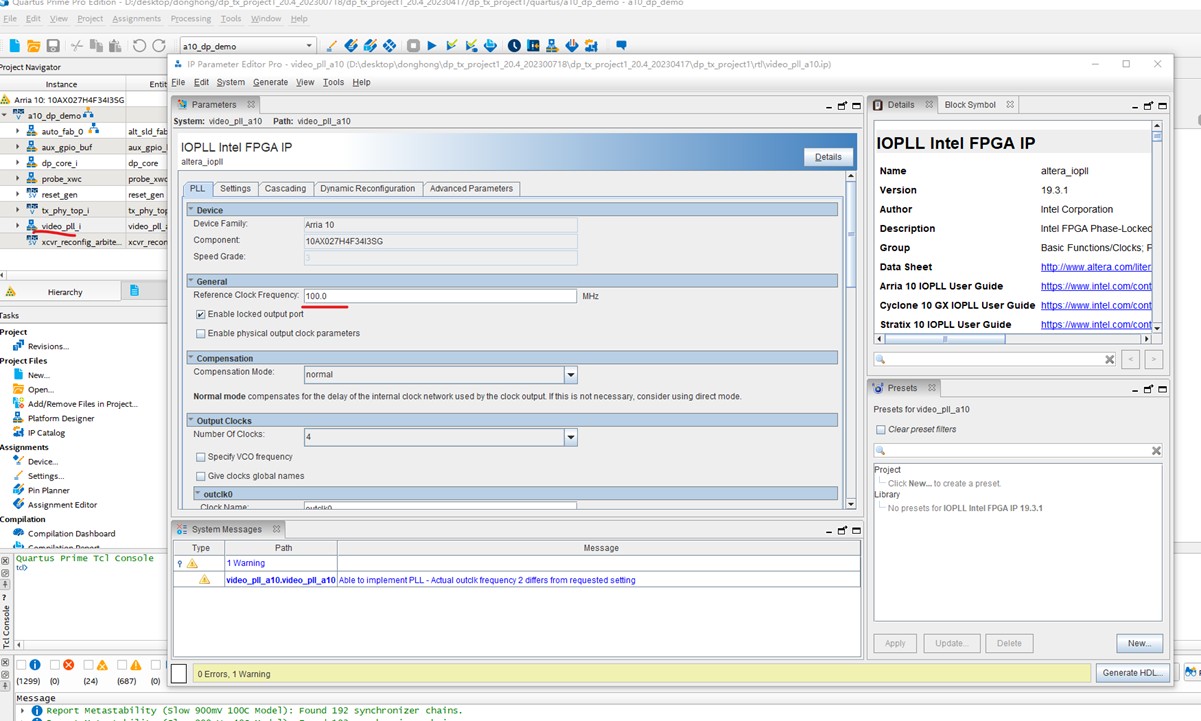

需要注意,由于新板子是 100MHz,需要把下面的 PLL 时钟改成 100MHz。对应工程为 dp_tx_project1_20.4_202300718 和 dp_tx_project2_20.4_202300718,如下图 (图6) 所示:

四、软件下载调试与屏幕点亮验证

1、下载 SOF 文件:通过 Quartus Programmer 将编译后的 SOF 文件下载至 FPGA。

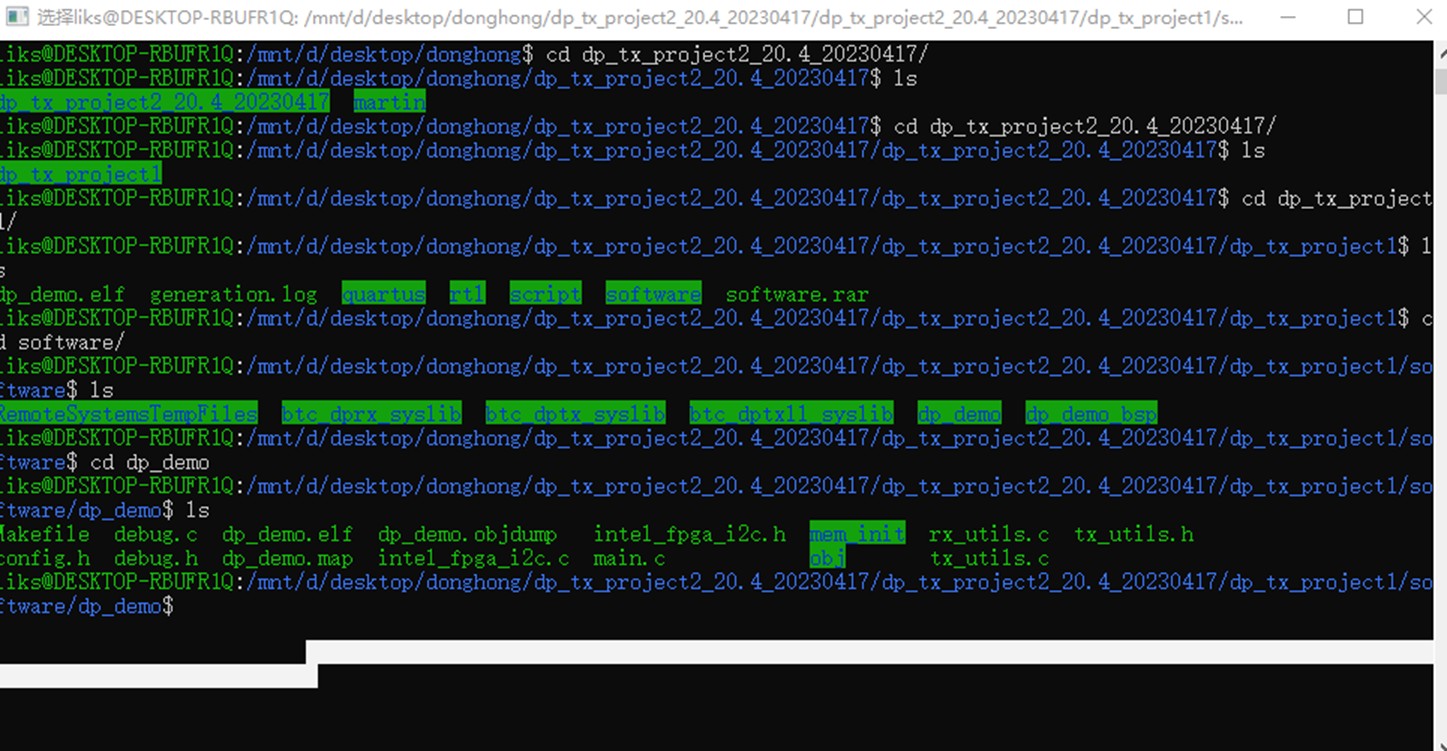

2、打开 Nios II Command Shell,定位到工程目录 /dp_demo 文件夹下。下图 (图7) 为 Nios II Command Shell 路径设置示意图,显示命令行中切换至工程目录的操作。

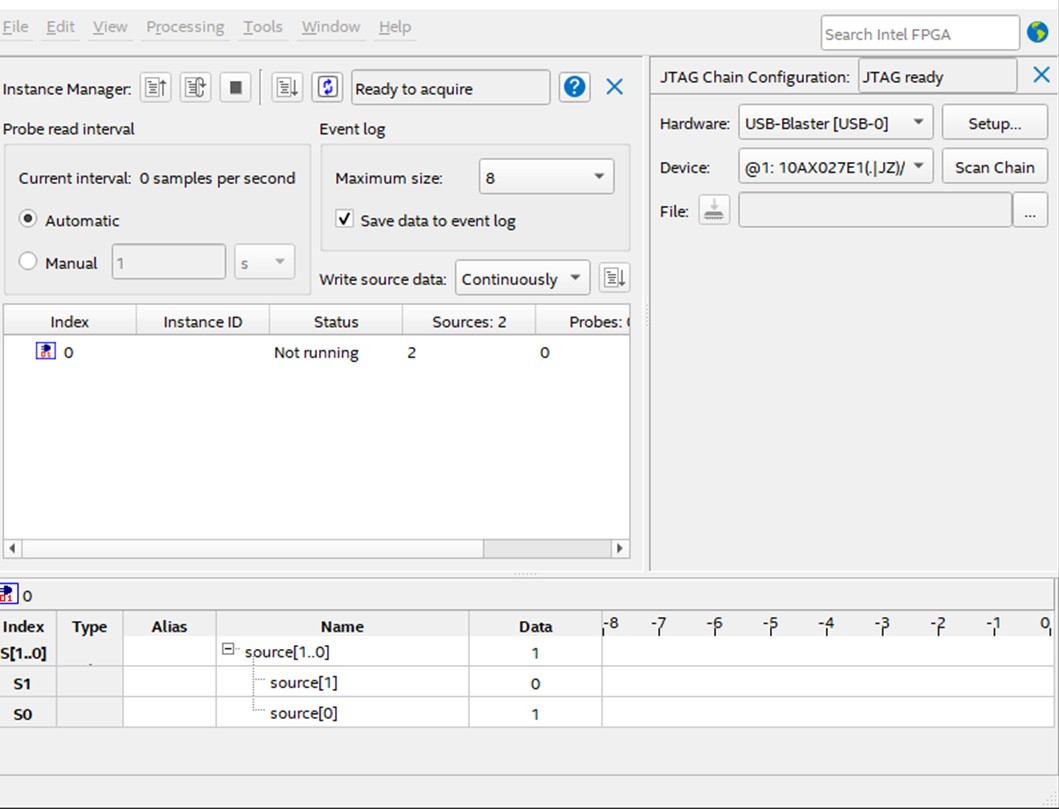

3、修改 Probe 设置:如下图 (图8),将调试选项中的 probe 值改为 1,以启用调试输出,该 probe 主要为了控制 DP 核的启动,方便调试,实际应用中可以省略。

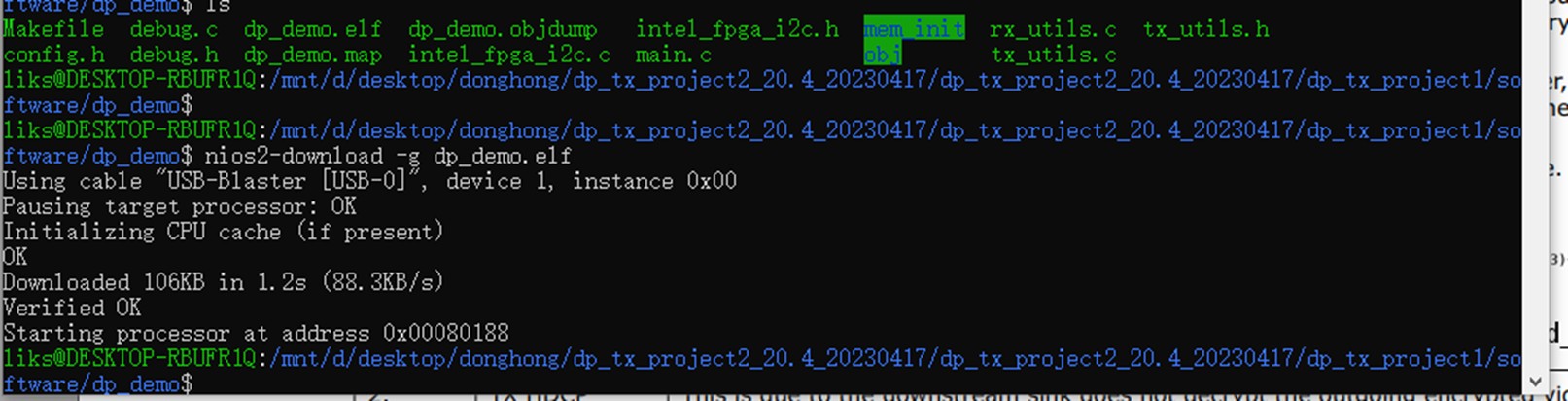

4、执行 nios2-download -g dp_demo.elf,如下图 (图9) 所示:

5、执行 nios2-terminal.exe,查看系统打印信息,确认程序是否正常运行。

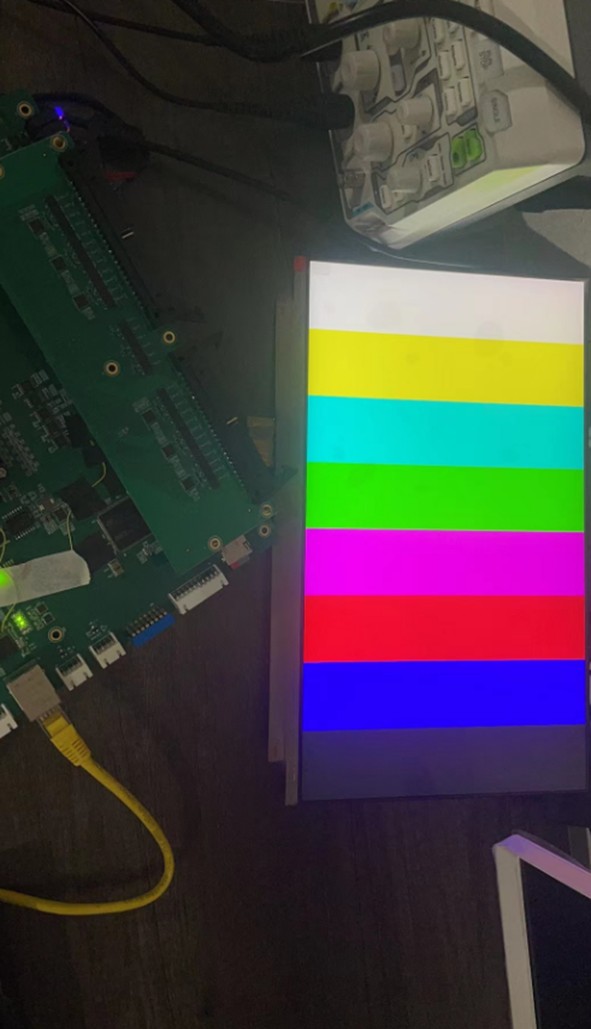

6、若一切配置正确,执行完上述步骤后,连接好的 Display Port 屏幕应成功点亮,下图 (图10) 为屏幕点亮的效果示意图:

五、总结

本文介绍了在 Altera Nios II Eclipse 中,完成 DP 工程的编译、软件下载与屏幕点亮的过程。内容涵盖环境配置、工程导入、代码编译、硬件配置等关键步骤,旨在为开发工程师提供实用的技术参考。

欲了解关于更多 Altera 相关方案或技术信息,请与骏龙科技当地的办事处联系或点击下方「联系我们」,提交您的需求,骏龙科技公司愿意为您提供更详细的技术解答。