概述

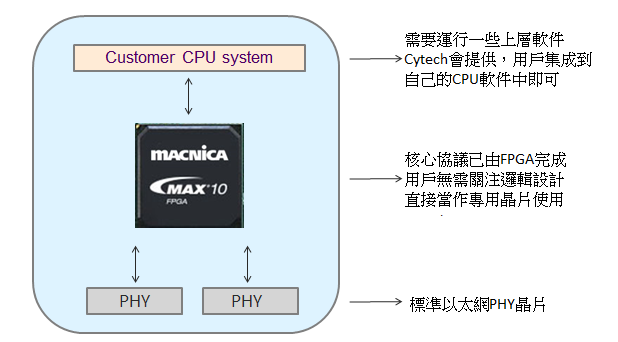

EtherCAT商業主站和開源主站,都是使用軟體的方法實現主站功能,主站的性能很大程度上取決於PC的性能和作業系統的實時性。而駿龍科技將EtherCAT的協議層用FPGA邏輯實現,預先編程好,客戶只需當作專用晶片使用。

EtherCAT Master ASSP晶片實現了標準的EtherCAT主站協議,採用標準的通用並行總線接口,可以連接任何CPU,並對晶片進行控制。支援ARM處理器或者x86處理器平台。提供參考軟件代碼,API函數,XML文件初始化系統等軟件。可用於任何標準的 EtherCAT 電機、IO設備的控制。

特點

• 支援ARM處理器上裸機程式運行EtherCAT主站,無需操作系統;

• 支援x86處理器,PCIe接口,提供Linux(withXenomai實時內核)下的驅動和應用程式的參考代碼;

• 友好的系統調試介面;

• CPU負擔小,無論高端或低端處理器,都能快速實現高實時性能的EtherCAT主站通信;

• 主站與從站間的同步性能強,同步時間的抖動遠小於1us(4軸實測50ns);

• 循環週期短,可以輕鬆實現31.25us的通信週期(可實現4軸62.5us的循環週期);

• 通過XML文件輕鬆配置系統,可接從站數量多

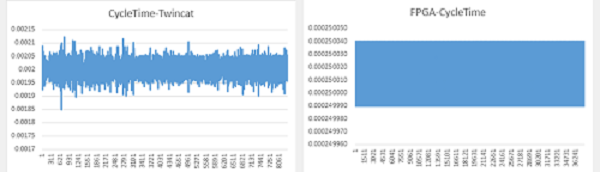

性能對比

| Twincat 評估版 (Intel Core I5) | 專用主站晶片方案(ARMA9+FPGA) |

| 循環周期2ms,發包的抖動±150us | 循環周期250us,發包時間幾乎無抖動 (循環周期和具體應用有關,此處結果僅是我們做的4軸電機/ARM進行軟件補插的一個例子,如果不考慮補插延遲,可以做到31.25us) |

| 只能使用第一個從站去同步主站 | 在FPGA內進行了同步處理,使用FPGA主站去同步所有從站 |

歡迎有興趣的客戶聯繫駿龍科技各地辦事處瞭解詳情,或發郵件至 stonemao@macnica.com,也可以關注微信號後直接微信留言。駿龍科技網站也可以留言。

駿龍科技微信號: