浅析 DDS 直接数字频率合成技术

直接数字频率合成技术 (Direct Digital Synthesis),简称 DDS,它是一种基于数字电子电路的频率合成技术,用于产生周期性波形。通常应用在一些频率激励 / 波形发生、频率相位调谐和调制、低功耗 RF 通信系统、液体和气体测量;还有接近度、运动和缺陷检测等传感器场合也可以找到 DDS 的身影。总体而言,目前从低频到几百 Mhz 的正弦波、三角波产生,绝大多数都使用了 DDS 芯片。本文将引领大家更进一步地了解 DDS。

DDS 的核心思想

对于一个正弦波来说,通常情况下其幅值可用以下公式得出:

A(t) = sin(ωt)

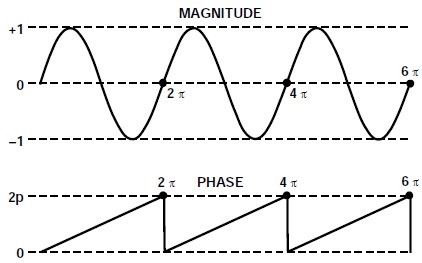

不过,这类正弦波是非线性曲线,因此除非通过分段构建,否则不易生成。另一方面,角度信息本质上是线性的。也就是说,每个单位时间内,相位角度会旋转固定角度。角速率取决于信号频率,也即 ω= 2πf。正弦波幅值和相位随时间的变化,如下图 (图1) 所示:

已知正弦波的相位是线性的,如果给定参考时间间隔 (时钟周期),则可以确定该周期内的相位旋转情况。

ΔPhase = ωΔt,求出 ω,ω = ΔPhase/Δt = 2πf

求出 f,并用参考时钟频率替换参考周期 (1/ fMCLK = Δt)

f = ΔPhase × fMCLK/2π

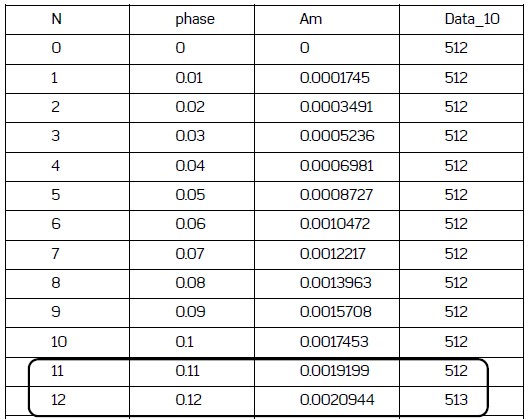

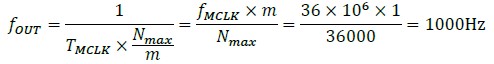

该如何理解上述的核心思想,我们来举一个简单的例子:先假设 DDS 有一个固定时钟,MCLK,为 36Mhz,那么每个脉冲的周期为 27.78ns。有一个正弦波的 “相位-幅度” 表,具有足够细密的相位步长,0.01°;那么一个完整的正弦波表就需要 36000 个点。完整的正弦波相位幅值表,如下图 (图2) 所示:

从上图 (图2) 可以看到,从相位 0° 开始,一直到相位 0.11°,虽然正弦波的幅值一直在增加,但是时钟没有增加到全幅度的 1/1024,因此 DAC 输出的都为一样的值。可以想象这 36000 个点记录了一个标准正弦波的全部。显然,36000 个 CLK 为正弦波的周期,即 1ms,其频率为 1kHz:

DDS 的核心思想就建立在此公式上:改变步长输出 m,可以改变输出频率。

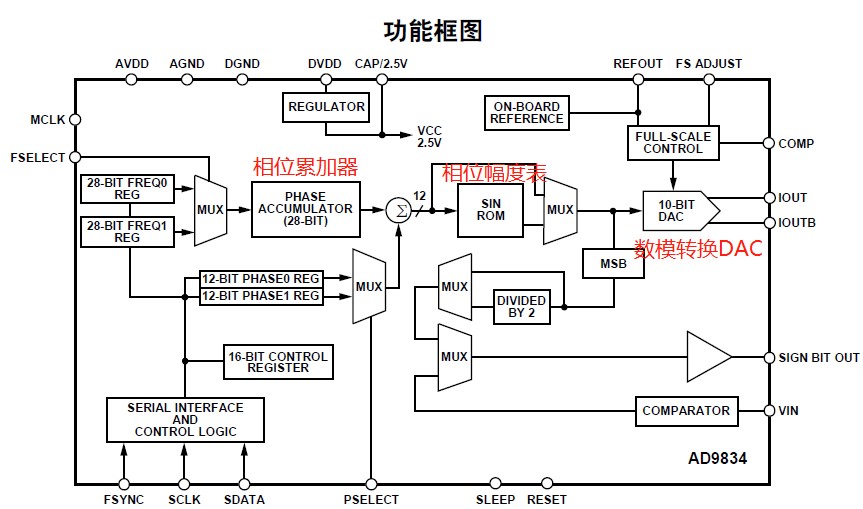

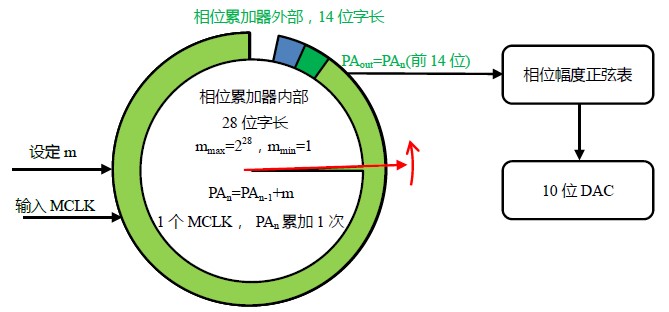

DDS 的组成内核

DDS 技术的核心由相位累加器 PA、相位幅度表和数模转换器 DAC 组成。我们以 AD9834 为例,调谐字最大可以达到 2^28=268435456 个点,远比上面我们说的 36000 个点要多,说明实际的 DDS 在相位分辨率上比 0.01° 要小得多。 AD9834 功能框图,如下图 (图3) 所示:

输入一个技术步长 m,外部 MCLK 出现一个脉冲,PA 完成一次累加。那么完成一个周期 360° 旋转,需要时间为:

![]()

因此输出正弦波频率为:

![]()

有了上文的理论铺垫,我们可以得出一个 DDS 的完整工作流程,如下图 (图4) 所示:

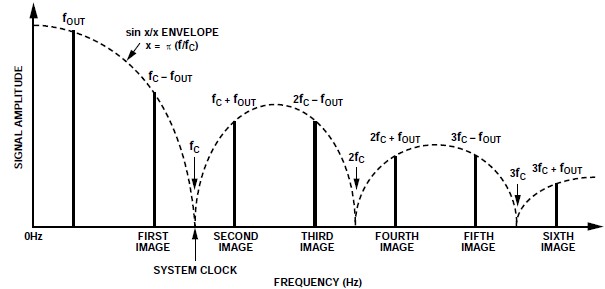

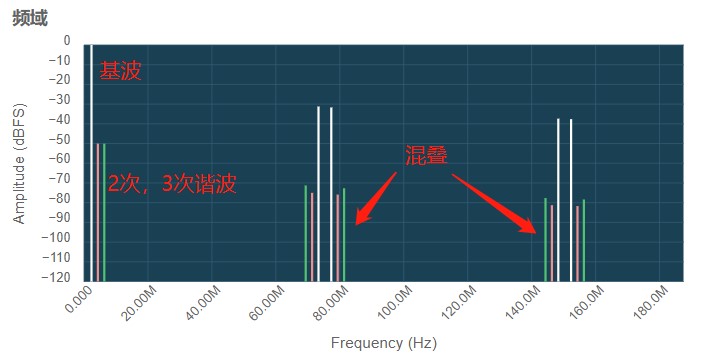

DDS的混叠现象

DDS 的输出是根据奈奎斯特采样原理进行采样的信号,输出的信号频率相当于需要采样的信号,而输入的 MCLK 相当于采样频率。具体而言,其输出频谱包含基波和混叠信号 (镜像),且镜像频率为参考时钟频率和所选输出频率的倍数。DDS 输出频谱,如下图 (图5) 所示:

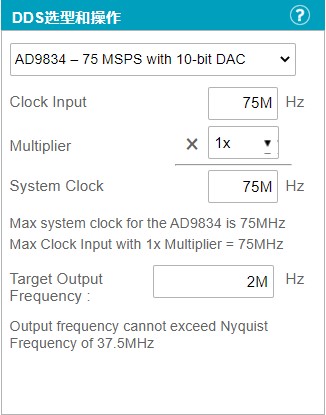

通过 ADI 官网的 DDS 仿真工具能够直观地看出混叠对 DDS 输出信号的影响。使用 AD9834 仿真输入输出选项,如下图 (图6) 所示:

使用 AD9834 输出频域,如下图 (图7) 所示:

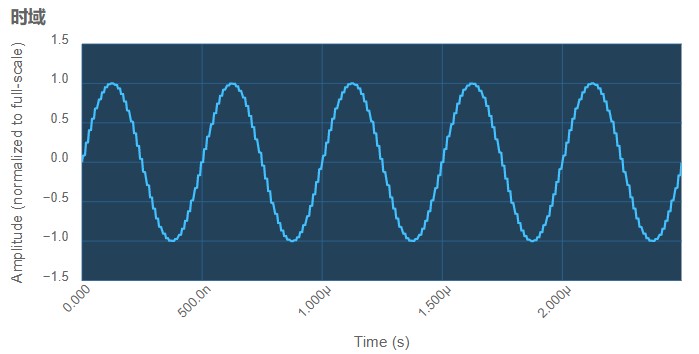

使用 AD9834 输出时域,如下图 (图8) 所示:

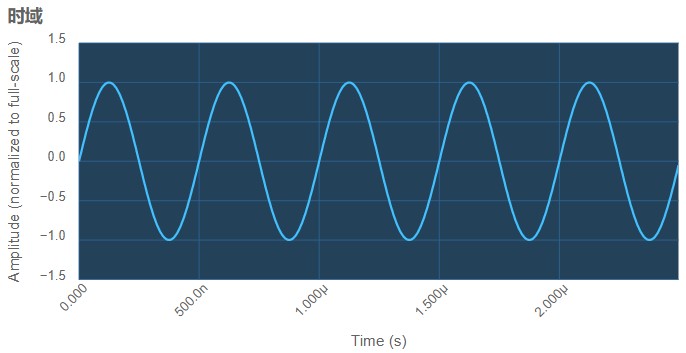

可以看出,由于混叠信号的影响,输出的 2Mhz 正弦波存在很大程度的失真,但混叠可以通过滤波器进行改善。以下我们来试试,设置 DDS 后端滤波器,如下图 (图9) 所示:

此时 DDS+ 低通滤波器后输出时域,如下图 (图10) 所示,输出的 2Mhz 正弦波已有改善。

总结

本文介绍了 DDS 的核心思想,DDS 的主要组成部分、以及使用 DDS 常见的信号失真导致原因。关于 DDS 更深层次的学习,比如 DDS 杂散问题,我们将会在未来的文章中与大家探讨。欲了解更多技术细节和 ADI 相关方案,您可以点击下方「联系我们」,提交您的需求,我们骏龙科技公司愿意为您提供更详细的技术解答。

参考资料

AN-837: DDS-Based Clock Jitter Performance vs. DAC Reconstruction Filter Performance

ADIsimDDS (Direct Digital Synthesis)