Intel Stratix10 H-tile 高速口的速率重配

Stratix10 概述

Intel Stratix10 为 Intel 14nm 器件,它采用了新的 Hyperflex™ FPGA 架构,与前一代高端 FPGA 相比,时钟频率提高了 2 倍,功耗降低了高达 70%。单个芯片最多集成 144 个高速收发器,数据速率高达 57.8 Gbps PAM-4 和 28.9 Gbps NRZ。DDR4 内存带宽高达 287.5 Gbps,速率最高为 2666 Mbps。HBM2 内存带宽高达 512 Gbps。PCI Express 硬核和软核 IP 支持 (高达 Gen4 x16,每通道 16 GT/s) 。

Intel 超级通道互连 (Intel UPI or CXL) 硬核 IP 包含 20 个传输速度为 11.2 GT/s 的通道。Intel Stratix 10 SoC 具备最高 1.35 GHz 的 64 位四核 ARM Cortex-A53、arm 外设、和支持 30 Gbps 速率直接连接的 FPGA。

根据不同的应用需求和技术侧重点分为 6 个子系列,分别为 Stratix10 GX、Stratix10 SX、Stratix10 TX、Stratix10 MX、Stratix10 DX、和 Stratix10 NX。

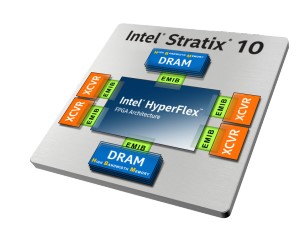

Intel Stratix 10 FPGA 和 SoC 采用了异构 3D 系统级封装 (SiP) 集成技术,通过多 Die 互联技术 (Embedded Multi-die Interconnect Bridge,EMIB) 将 FPGA 的 Fabric 和高速口 Die 以及片内 DRAM HBM2 Die 互联,极大地方便了不同 Die 之间的组合。该器件如下图 (图1) 所示:

Intel 高速口 Die 根据速率和功能又分为 L-tile、H-tile、E-tile 和 P-tile,具体不同 Tile 的特点,如下表 (表1) 所示:

| 特性 | 收发器变体 | |||

| Tile | L-tile (17.4G) Pcie Gen3 X16 |

H-tile (28.3G) PCIe Gen3 X16 |

E-Tile (30G/58G) 4X 100GE |

Intel 超级通道互联 (IntelUPI) PCIE Gen4 X16 |

| Intel Stratix10 变体 | GX SX | GX SX TX MX | TX MX | DX |

| 单Tile最大收发器数量 | 24 | 24 | 24 | 20 |

| 芯片至芯片最大速率 (NRZ/PAM4) | 17.4Gbps | 28.3Gbps | 28.9Gpbs/57.8Gbps | 16GT/s/- |

| 背板最大数据速率 | 12.5Gbps | 28.3Gbps | 28.9Gpbs/57.8Gbps | 16GT/s/- |

| 数据速率最大时的插入损耗 | 最高 18dB | 最高 30dB | 最高 35dB | 参阅 PCIe Gen4 和 UPI 规格和条件 |

|

硬核IP |

PCIe Gen1、2、3包括支持X1、X4、X8、X16 通道支持,10G FEC 硬核IP |

PCIe Gen1、2、3包括支持X1、X4、X8、X16 通道支持SR-IOV ;包括4个物理功能和2000个虚拟功能 10G FEC 硬核IP | 10/25/100Gbe MAC,支持 RS-FEC 和 KP-FEC | PCIe Gen1、2、3、4包括支持X1、X4、X8、X16通道;支持SR-IOV,以及8个物理功能和2008个虚拟功能;端口分叉支持 2x8 端点或 4x4 根端口事务层(LT) 旁路功能;通过协议配置(CvP) 初始化,自主模式 VirtIO,可扩展 IOV 共享虚拟内存 |

表1 不同高速口 Tile 之间的特性

Stratix10 H-tile 简介

H-tile 封装和分布

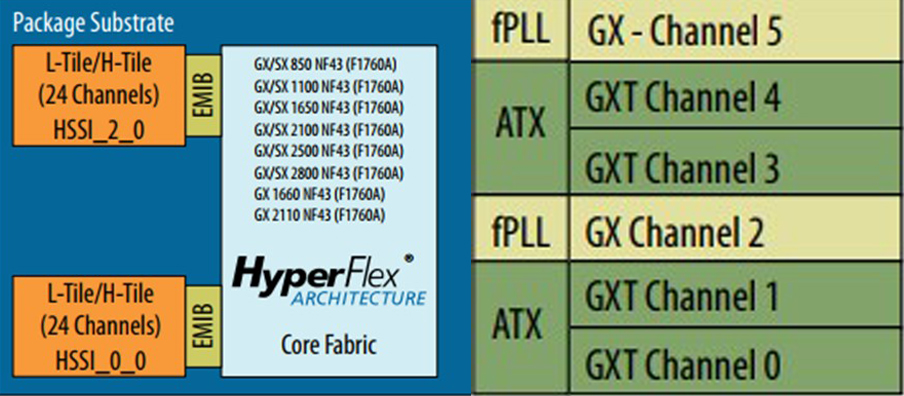

以 48 个高速口通道的 NF43 封装举例,其他封装结构类似。下图 (图2) 是 NF43 封装的 Stratix10,有 2 个高速收发器口 Tile,每个 Tile 包含 4 个 BANK,每个 bank 包含 6 个收发通道,即一个 Tile 有 24 个收发器通道。

通道 0、1、3、4 为 GXT,通道 2、5为 GX 通道,并且 GXT 通道可以当作 GX 通道使用。其中 GXT 通道最大速率为 28.3Gbps,GX 通道最大速率为 17.4Gbps。高速口通道通过 EMIB 与 FPGA 的 Core Fabric 相连。

H-tile 时钟网络

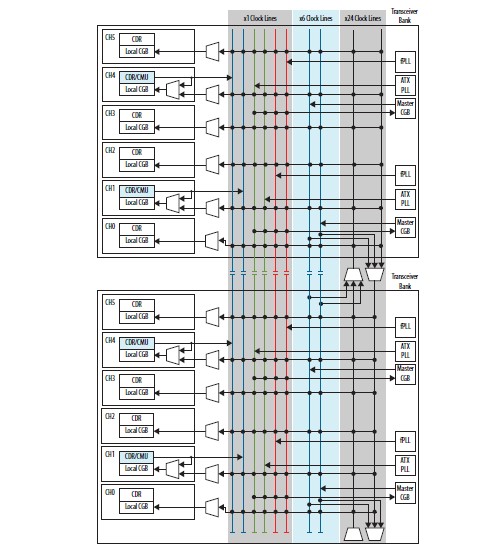

每个高速口 BANK 包含 6 个高速口通道,有 2 个高性能 ATX PLL,2 个 fPLL,2 个 CMU PLL,2 个 Master CGB (clock generation block),支持 X1,X6,X24 和 GXT 时钟网络。Stratix10 H-tile 时钟网络,如下图 (图3) 所示:

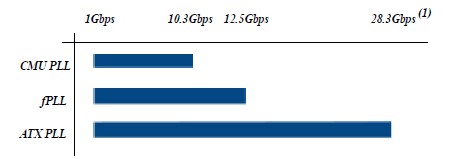

一般 12.5Gbps 速率以上用 ATX PLL,12.5Gbps 以下用 fpll,10Gbps 以下可以用 CMU PLL。PLL 支持的速率,如下图 (图4) 所示:

H-tile Transceiver PHY 架构

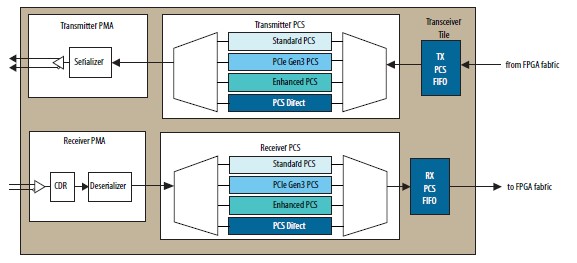

H-tile 的 Transceiver PHY 主要包括模拟前端 (Physical Medium Attachment) MA 和数字编码层 PCS。其中 TX PMA 主要由并转串和传输 Buffer 组成,RX PMA 主要由数据恢复单元 CDR、接收 Buffer 和串并转换模块组成。

Stratix 10 Transceiver PHY 支持四种类型的 PCS:

- Enhanced PCS

- Standard PCS

- PCI Express Gen3 PCS

- PCS Direct

GX 通道 PCS ,如下图 (图5) 所示:

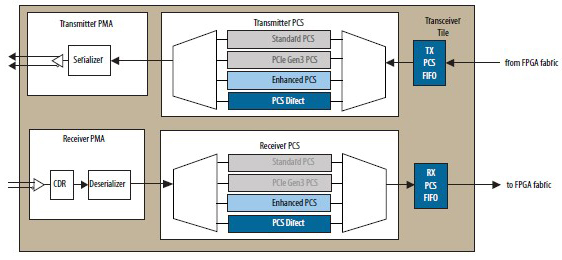

GXT 通道支持两种 PCS:Enhanced PCS 和 PCS Direct。GXT 通道,如下图 (图6) 所示:

不同的 PCS 类型支持的最大速率不一样,GX 通道最大速率可以达到 17.4Gpbs,如下表 (表2) 所示:

| PCS Type | L-Tile Production | H-Tile Production | |||

| -2 Speed Grade | -3 Speed Grade | -1 Speed Grade | -2 Speed Grade | -3 Speed Grade | |

| Standard PCS | 12 Gbps(3) or 10.81344 Gbps(4) | 9.8304 Gbps(4) | 12 Gbps(3) or 10.81344 Gbps(4) | 12 Gbps(3) or 10.81344 Gbps(4) | 9.8304 Gbps(4) |

| Enhanced PCS | 17.4 Gbps | ||||

| PCIe Gen3 PCS | 8 Gbps | ||||

| PCS Direct | 17.4 Gbps | ||||

表2 GX 通道 PCS 速率

GXT 通道在 H-tile 可以达到 28.3Gbps,如下表 (表3) 所示:

| PCS Type | L-Tile Production | H-Tile Production | |||

| -2 Speed Grade | -3 Speed Grade | -1 Speed Grade | -2 Speed Grade | -3 Speed Grade | |

| Enhanced PCS | 26.6 Gbps | No GXT | 28.3 Gbps | 26.6 Gbps | No GXT |

| PCS Direct | 26.6 Gbps | No GXT | 28.3 Gbps | 26.6 Gbps | No GXT |

表3 GXT 通道速率

Stratix10 H-tile 动态重配

H-tile 动态配置

Stratix10 高速口支持在器件运行过程中,为满足一些需要更改高速口配置的应用,会对收发器通道和相关的 PLL 进行动态配置。它提供了基于 Avalon 协议的动态配置接口。用户侧可根据需求对高速口速率切换,信号完整性微调,enhanced 和 standard PCS 切换,PLL 切换等进行配置。H-tile 支持的动态配置的特性,具体如下表 (表4) 所示:

| Reconfiguration | Features |

| Channel Reconfiguration | PMA analog featuresVoD - VOD - Pre-emphasis - Continuous Time Linear Equalizer (CTLE) - Decision Feedback Equalization (DFE) - Variable Gain Amplifier (VGA) |

| TX PLL - TX local clock dividers - TX PLL switching |

|

| RX CDR - RX CDR settings - RX CDR reference clock switching |

|

| Reconfiguration of PCS blocks within the datapath | |

| Datapath switching - Standard, Enhanced, PCS Direct |

|

| PLL Reconfiguration | PLL settings - Counters |

| PLl reference clock switching |

表4 H-tile 支持的动态配置

Avalon-mm 动态配置

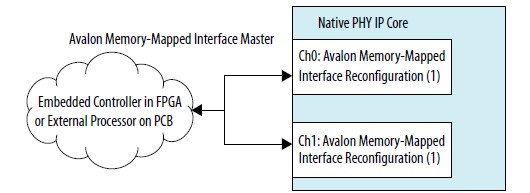

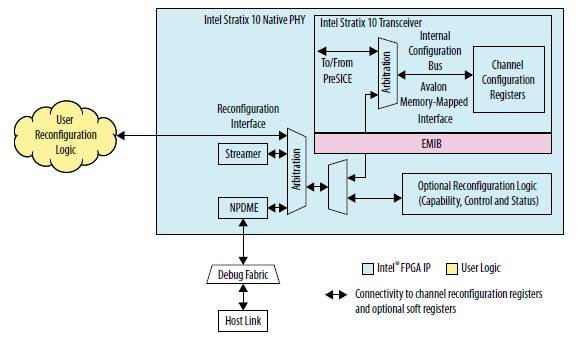

一个 PLL 最多由一个重配置接口,但是 native PHY IP 可以指定多个通道进行配置。每个通道能使用专用的单个重配置接口,也能共享一个重配置接口,对重配置接口必须符合 Avalon-MM 的读写操作规范。Avalon-MM 读写操作规范可参考具体 Avalon 协议。Avalon-mm 动态配置接口,如下图 (图7) 所示:

重配置接口的仲裁机制

重配置接口有两级仲裁机制:

- 第一级主要为用户重配逻辑、嵌入式重配流光器和 Debug 接口之间的仲裁

- 第二级为 Presice 校准引擎和重配接口之间的校准

第一级嵌入式流光器有最高的优先级,Debug 接口最低,而第二级 Presice 有最高的优先级。

仲裁机制如下图 (图8) 所示:

Intel Stratix 10 L-Tile / H-Tile 收发器 Native PHY 和 PLL IP 核 (可选) 允许您将 IP 实例指定的参数保存为配置文件。配置文件存储了特定的 IP 实例的地址和数据值,配置文件是在 IP 生成期间生成的。它们位于 <IP实例名称>/reconfig/IP 实例的子文件夹。配置数据提供以下格式:

- SystemVerilog packages: <name>.sv

- C Header files: <name>.h

- Memory Initialization File (MIF): <name>.mif

选择性地在相同的 Native PHY IP 和 / 或 PLL IP core Parameter Editors 中,让多种配置或设置档来执行动态重配置。它支持 IP Parameter Editor 创建、存储和分析多种配置或设置档的参数设置。

例如:Profile 0 的配置文件被存储在 <filename_CFG0.sv>。Native PHY / PLL IP 内核的每个实例每次可以创建多达 8 种重配置设置档 (Profile 0 - Profile 7)。

选择性地使 Native PHY 和 / 或 PLL IP 内核中的嵌入式重配置流光器,进行自动化重配置操作。嵌入式重配置流光器是一个功能模块,它可以执行 Avalon-MM 传输来访问接收器中的通道 / PLL 配置寄存器。

使用嵌入式流光器时,Native PHY / PLL IP 内核将会嵌入 HDL 代码,用于 IP 文件中的重配置设置档存储以及重配置控制逻辑。对于 Native PHY / PLL IP,通过重配置接口控制相应的寄存器,嵌入式流光器的控制和状态信号将映射到相应的寄存器中。

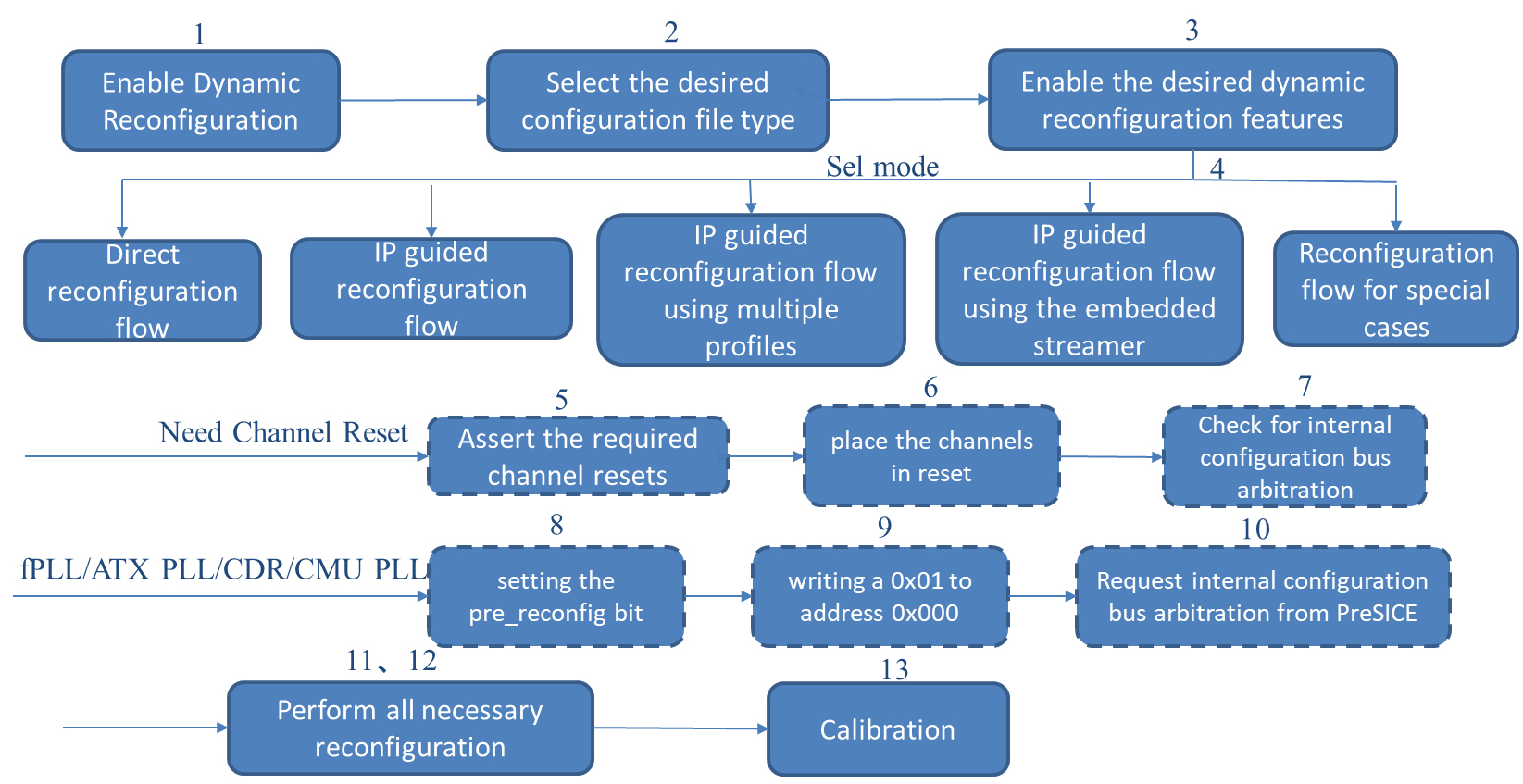

动态重配置的流程

动态重配置的流程主要是对 IP 的配置和寄存器读写操作,在写之前要遵循 read-modify-write 操作。它有三个配置模式:直接配置,IP 指导配置 (嵌入式配置流光器和 Profiles) 和特殊 cases 的配置。

实现动态重配置是用嵌入式流光器和 Profiles 进行配置,具体流程说明如下:

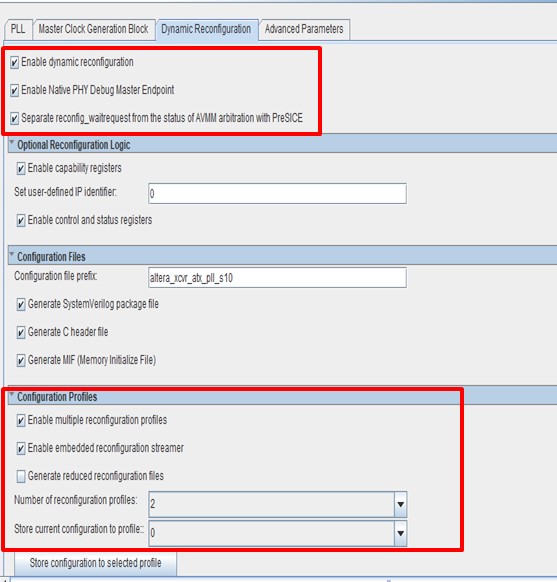

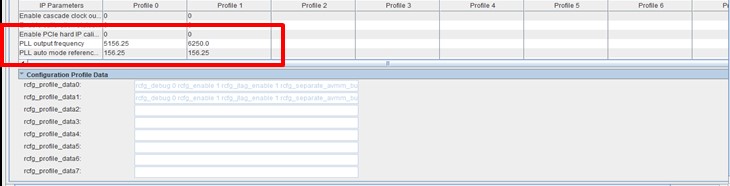

第一步:在 IP 配置中 Enable Dynamic Reconfiguration;

第二步:选择 IP 中所需的 IP 配置文件;

第三步:使能所需的动态重配功能和模式 (包括 Direct reconfiguration、IP guided reconfiguration、IP guided reconfiguration using multiple profiles、IP guided reconfiguration using the embedded streamer、 Reconfiguration for special cases) ;

第四步:通道置于数字复位;

第五步:如果重配置涉及到速率 / 协议 / PRBS 使能,将通道置于模拟复位;

第六步:如果使用了背景校准,通过设置偏移地址 0X542[0] 为 0x0 来禁用背景校准;

第七步:如果涉及到重配 PLL,通过设置 PLL 的 pre_reconfig bit 使 PLL 进入配置模式,对 PLL 进行动态配置,如 果没有直接进入所选的通道配置模式;

第八步:所有配置完成后进行重新校准。

具体动态重配置流程图,如下图 (图9) 所示:

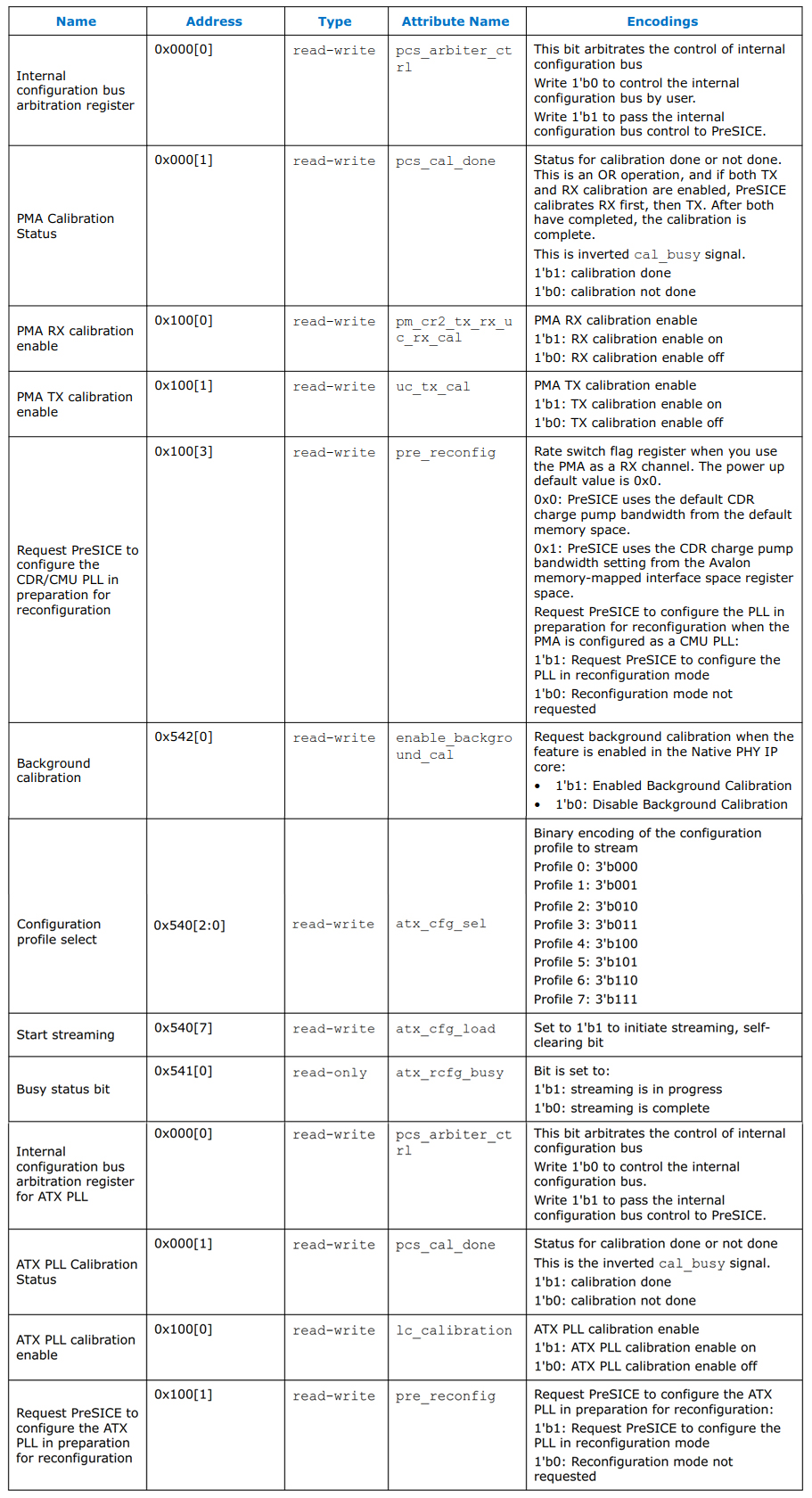

在重配过程中所用到的关键寄存器,如下图 (图10) 所示:

Stratix10 H-tile 的速率重配

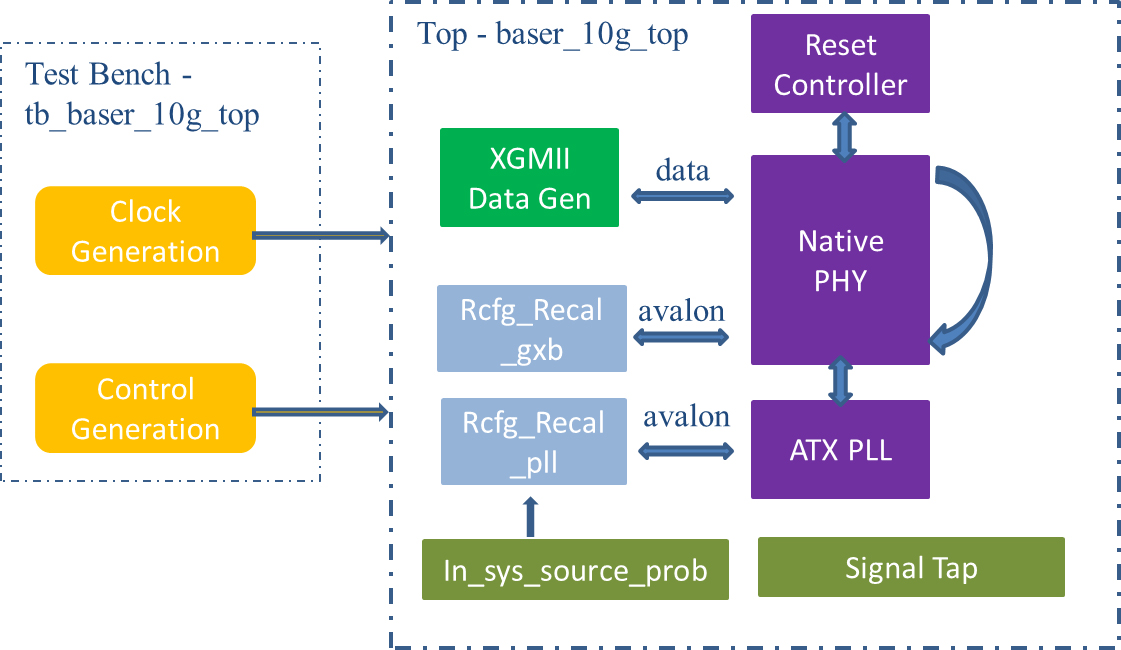

版本:Quartus Pro 21.1,Modelsim SE Start

工程功能:10G Baser 10.3125Gbps - 12.5Gbps 速率动态切换

具体功能模块图,如下图 (图11) 所示:

IP 配置如下图 (图12、图13、图14) 所示:

Stratix10 H-tile 重新校准的仿真验证

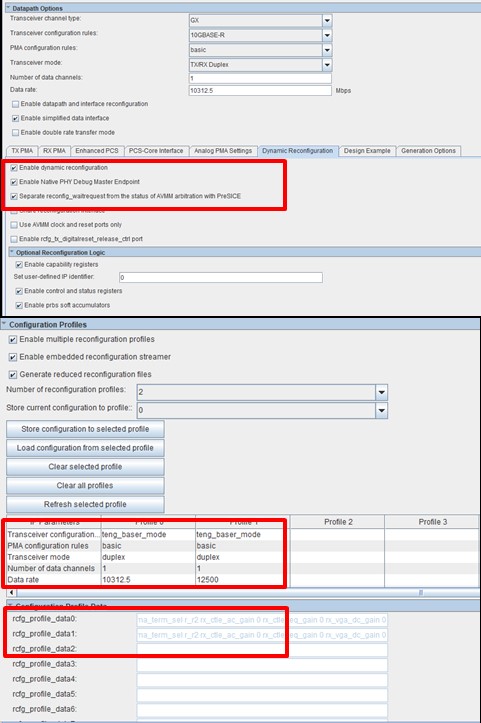

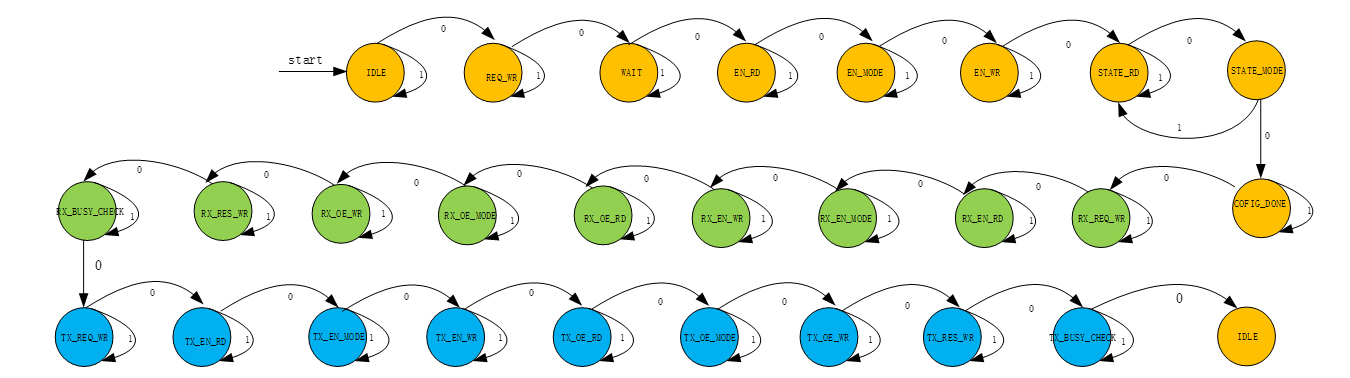

PLL 动态重配模块状态流程

第一步:写 010 到地址 100 进行 prepare pll;

第二步:写 001 到地址 000 返回到 presice,等待 busy 信号拉低;

第三步:写 010 到 000 请求用户重配控制;

第四步:540 进行 read-modify-write 操作,轮询读地址 541 的最低为直到最低位为 1 重配完成,返回控制权到 presice;

第五步:校准操作,同样执行 read-modify-write,等待校准完成返回控制全到 presice。控制到下一状态的信号为 waitrequste 信号。

具体 PLL 动态重配模块状态流程图, 黄色的部分为重配,绿色的部分为校准,如下图 (图15) 所示:

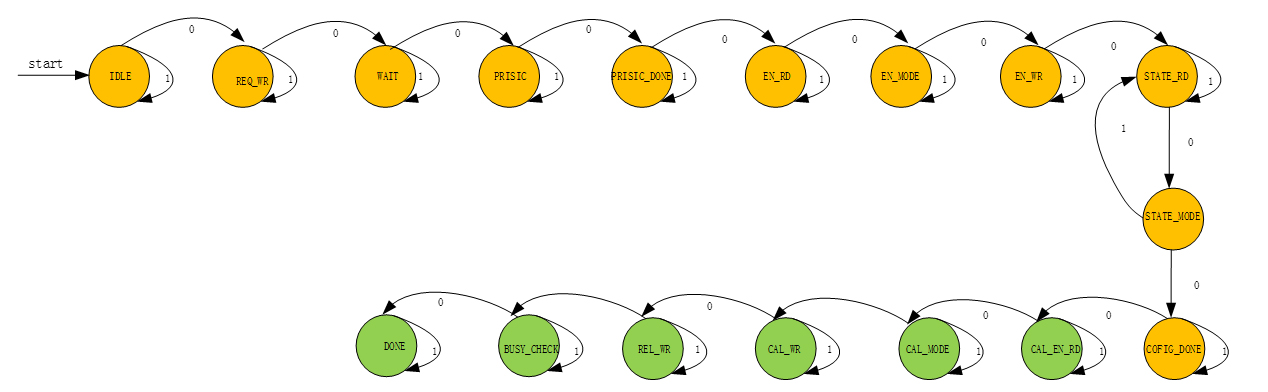

通道重配置模块状态流程

第一步:重配流程和 PLL 类似,只是少了 prepare Pll 阶段;

第二步:等重配完成,先执行 PMA RX 校准,再执行 PMA TX 校准,执行校准是需要对 481 地址进行开启和关闭相应 busy 信号。

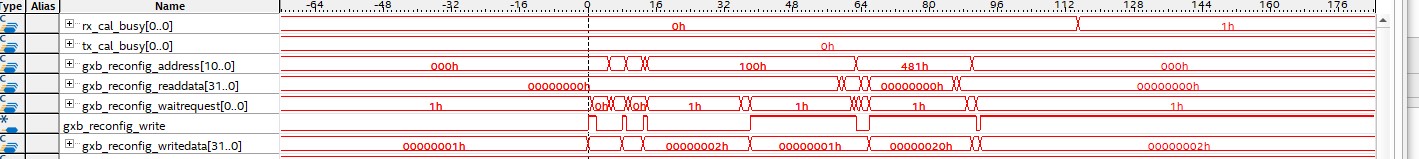

所有的写操作都严格按照 read-modify-write 进行,如下图 (图16) 所示:

通过仿真,我们看到 IP 配置的写操作全部按照 read-modify-write 流程,并且在配置完成之后 PLL 有失锁。在重新锁住的过程中,经过验证,当我们重配的速率与之前的速率有证书倍关系时,PLL 不会失锁。

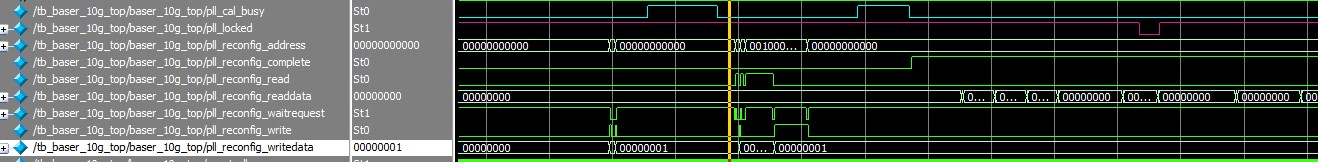

PLL 重配仿真,如下图 (图17) 所示:

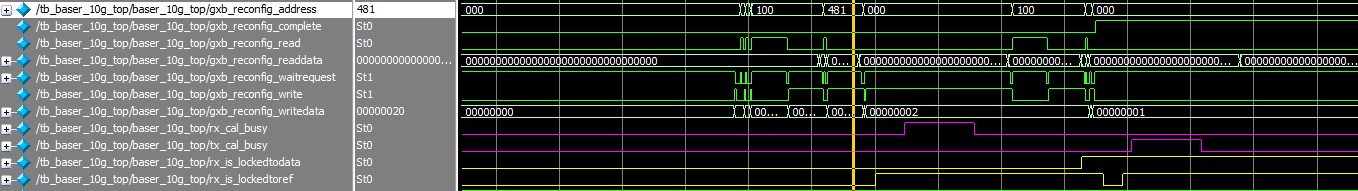

Native PHY 重配仿真,如下图 (图18) 所示:

重配后时钟速率变化,如下图 (图19) 所示:

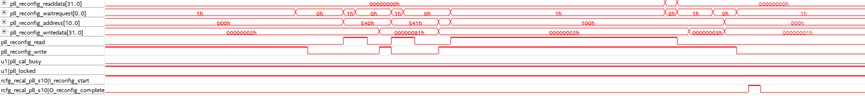

通过上板进行对比,与仿真结果一致。PLL重配上板结果,如下图 (图20) 所示:

Native PHY 重配上板结果,如下图 (图21) 所示:

总结

为了加深大家对 Stratix10 整体概念的理解,本文先介绍了 Intel Stratix10 系列不同高速口 Tile 的特性,用户可根据自身的需求选择不同的器件,保证更多的灵活性。之后重点介绍了 H-tile 的结构、时钟网络等,以及对 H-tile 的速率重配置做了功能仿真和上板验证。其他支持的重配置流程类似,工程师同样可根据自己的设计进行配置。欲了解更多技术细节和 Intel 相关方案,您可以点击下方「联系我们」,提交您的需求,我们骏龙科技公司愿意为您提供更详细的技术解答。