基于 Nios® V 处理器的 Agilex®7 Mailbox Client IP 应用实践 (上) — FPGA 多镜像切换

《基于 Nios® V 处理器的 Agilex®7 Mailbox Client IP 应用实践》系列专辑由两篇文章构成,主要介绍在 Altera Agilex® 7 FPGA 平台上,通过 Nios® V 处理器操作 Mailbox Client IP 实现 FPGA 多镜像切换,以及使用Nios® V 读取芯片 ID 和温度的参考方案。

本文为上篇,主要讲解硬件平台、软件系统的搭建以及 Nios® V 操作镜像切换的内容。下一篇将继续为大家介绍使用 Nios® V 读取芯片 ID 和温度的参考方案。

背景

目前 Altera 官方提供的编程例程,主要是基于 JTAG 到 Avalon 接口和配套的 TCL 脚本控制流程来实现对 QSPI Flash 的读写、擦除和编程。这种实现方式在实际应用中存在着一定的局限性,开发者无法直接使用。

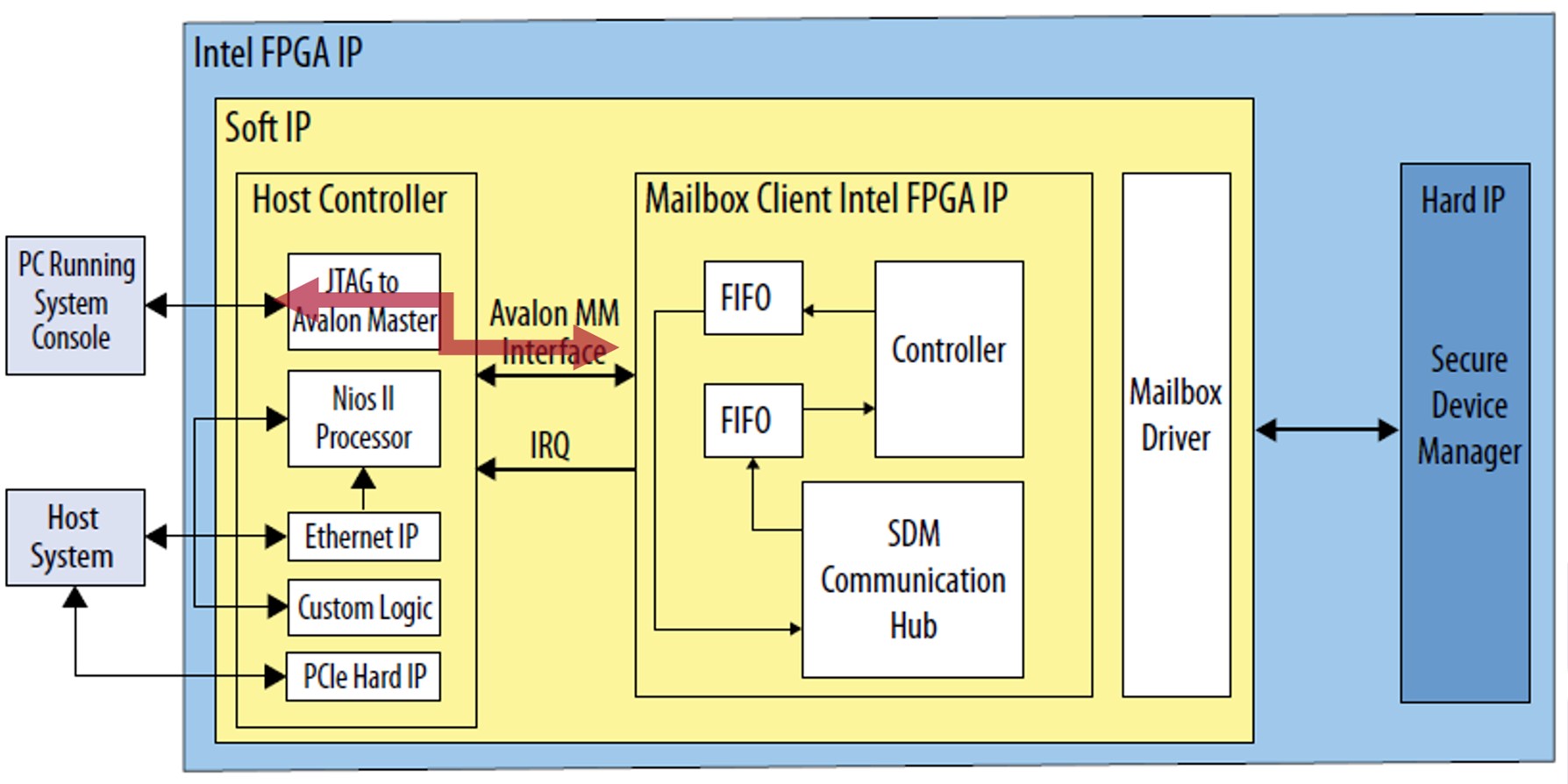

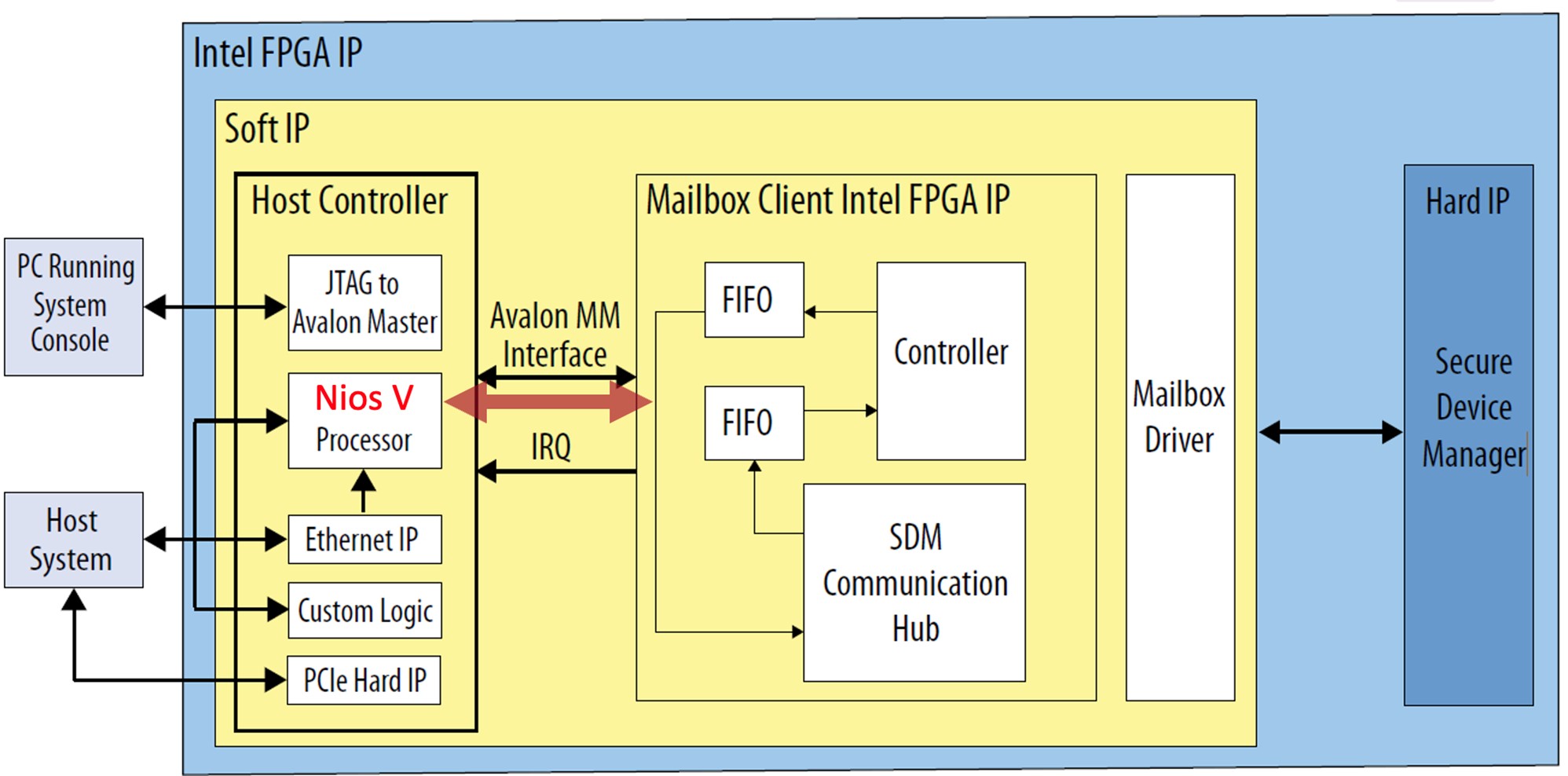

使用 RTL 操作Mailbox Client Altera FPGA IP 虽然移植方便,但操作复杂,且无参考例程;使用 Nios® V 操作 Mailbox Client Altera FPGA IP 虽然 Nios V 环境搭建复杂,但操作简单。下图 (图1)、(图2) 为两种方案的对比,红色箭头为关键命令通路。从图中可以看出,第二种方案更有优势。

硬件平台搭建

本次操作主要使用到的硬件配置如下:

- 硬件平台:DK-SI-AGF014EB (AGFB014R24B2E2V)

- 软件环境:Quartus 23.1

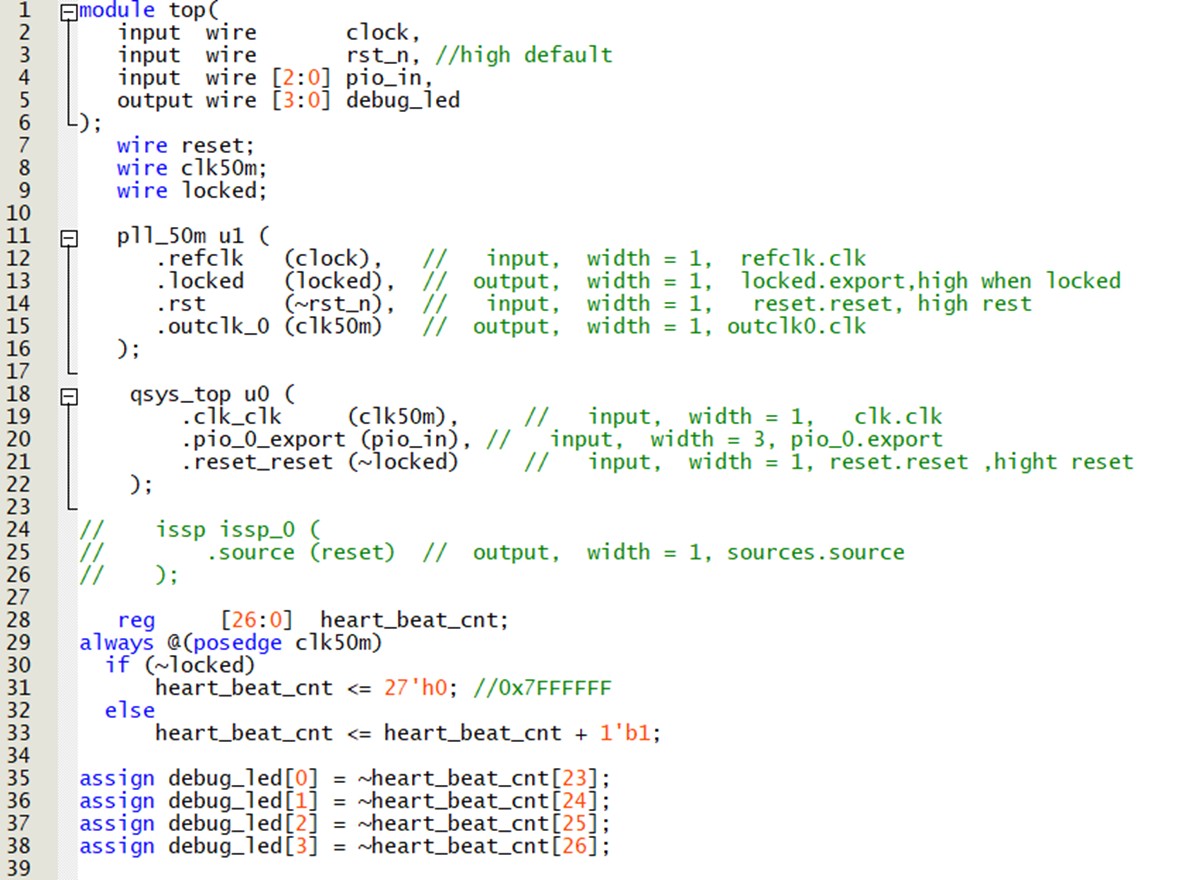

下图 (图3) 为硬件系统顶层架构设计图:

以下为关键接口及硬件引脚分配的说明:

时钟:100Mhz 输入 按键:用来切换镜像 LED 输出:用来区分不同镜像 Qsys:Nios® V 系统,Mailbox PIN_A44------rst_n, FPGA_PB7,S8按键 PIN_U52------clock, FPGA_SYSTEM_CLK, PIN_H45------pio_in[0] PIN_F45 ------pio_in[1] PIN_J44 ------pio_in[2] PIN_D43------debug_led[0] PIN_B43------debug_led[1] PIN_C42------debug_led[2] PIN_A42------debug_led[3]

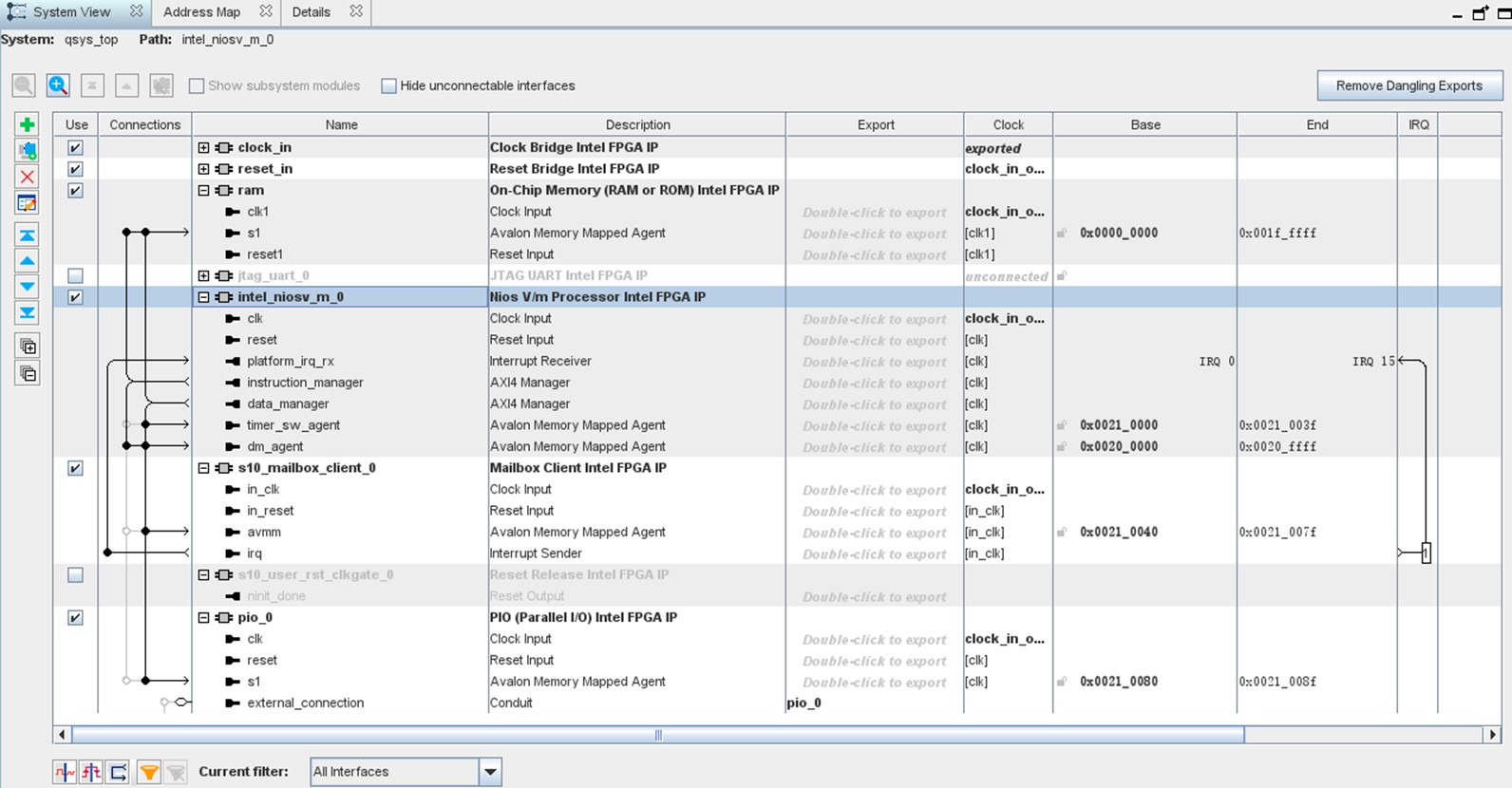

下图 (图4) 为 Qsys 设计:

Nios® V 软件系统搭建

核心组件为:Nios® V 软核、On-chip memory、Mailbox client IP、PIO intel FPGA IP、Jtag_uart IP。

(1) 按照 Qsys 的结构搭建系统,连接好信号,并分配好各模块地址 (可以在 address map 中自动分配)。

(2) 建议把 on-chip memory 的地址设置为起始 0x0000_0000。

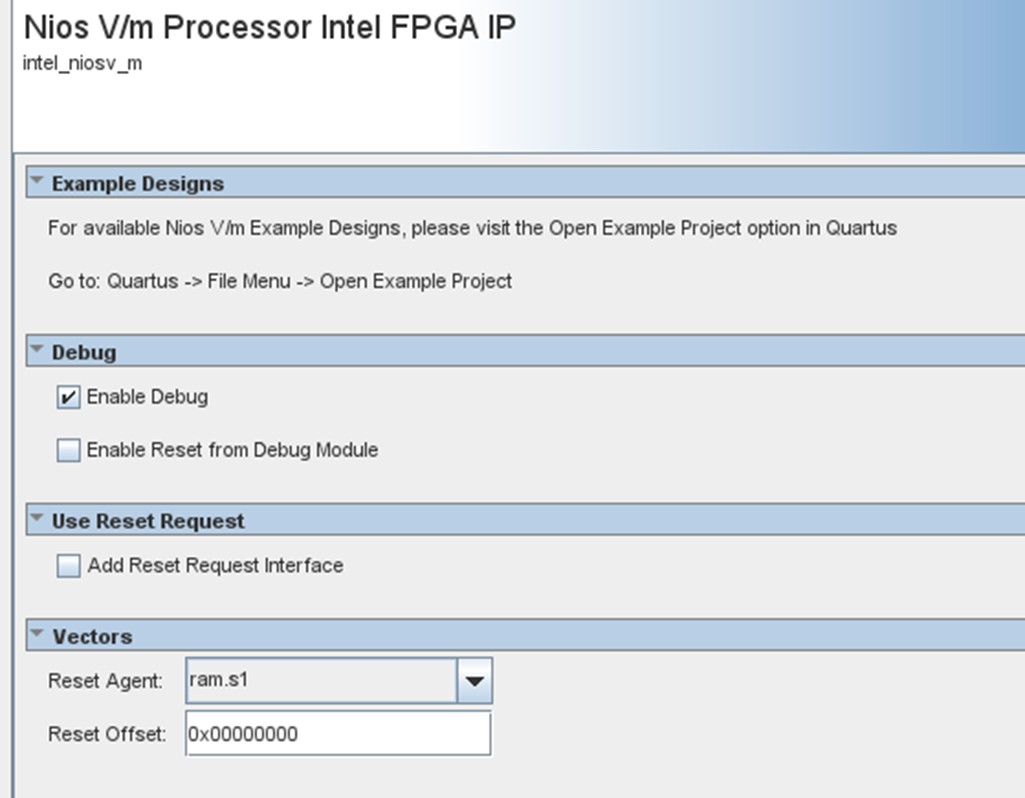

(3) Nios® V 中设置如下图 (图5),指定 on-chip memory。

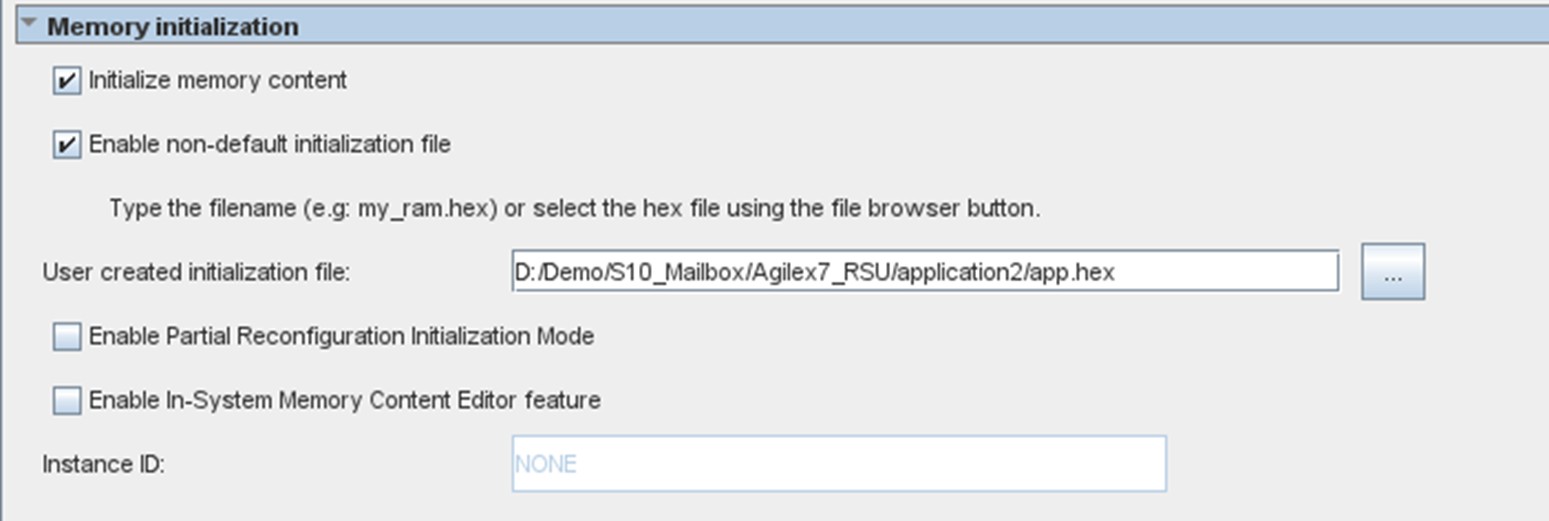

(4) On-chip memory 设置如下,指定代码 hex 位置。如果新建工程还没有 hex 文件,可以生成 hex 后再设置。

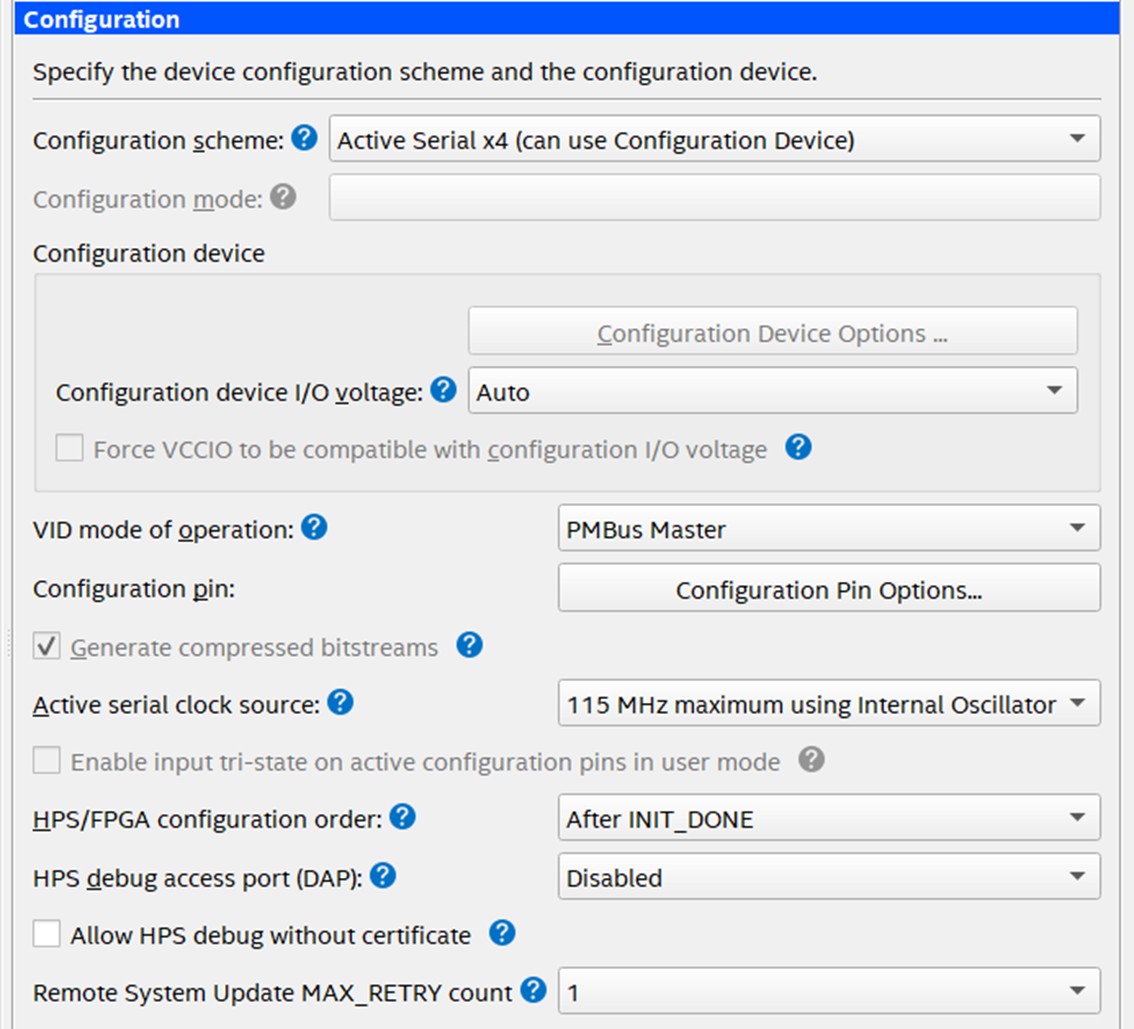

(5) Device and Pin Options 设置如下图 (图7):

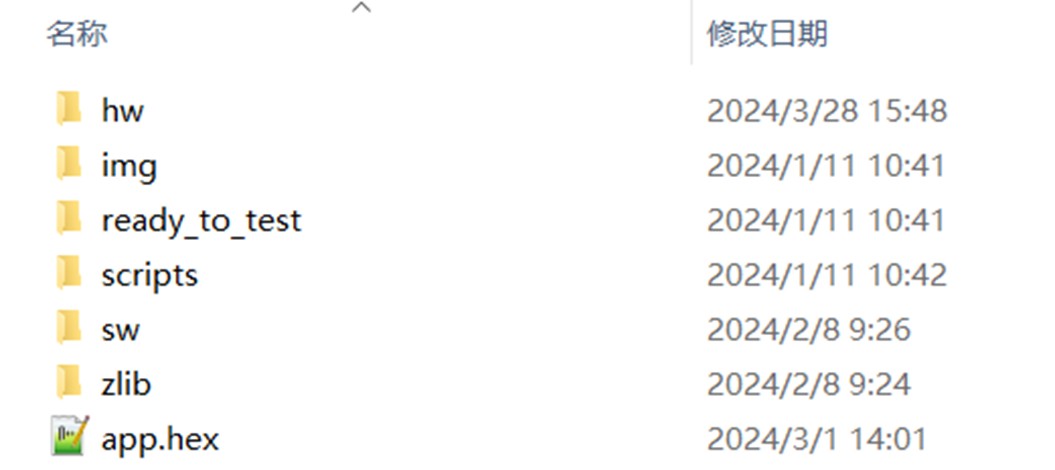

(6) 创建 ZLIB 库。LibRSU HAL API 需要 ZLIB 库,可点击此处下载,下载完成后放到工程目录 -> zlib文件夹。

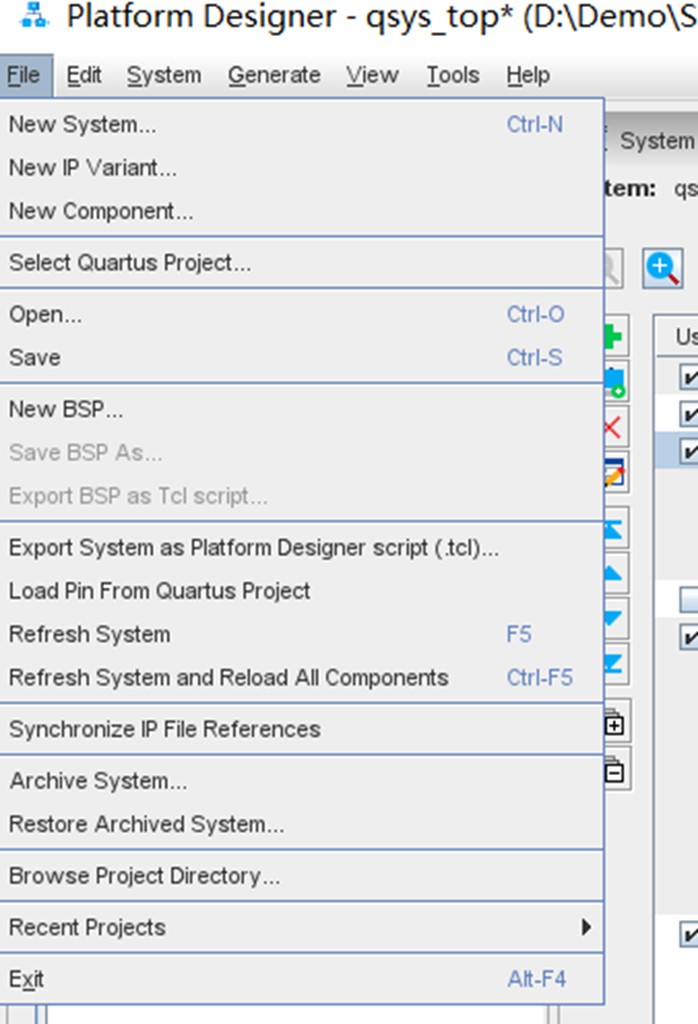

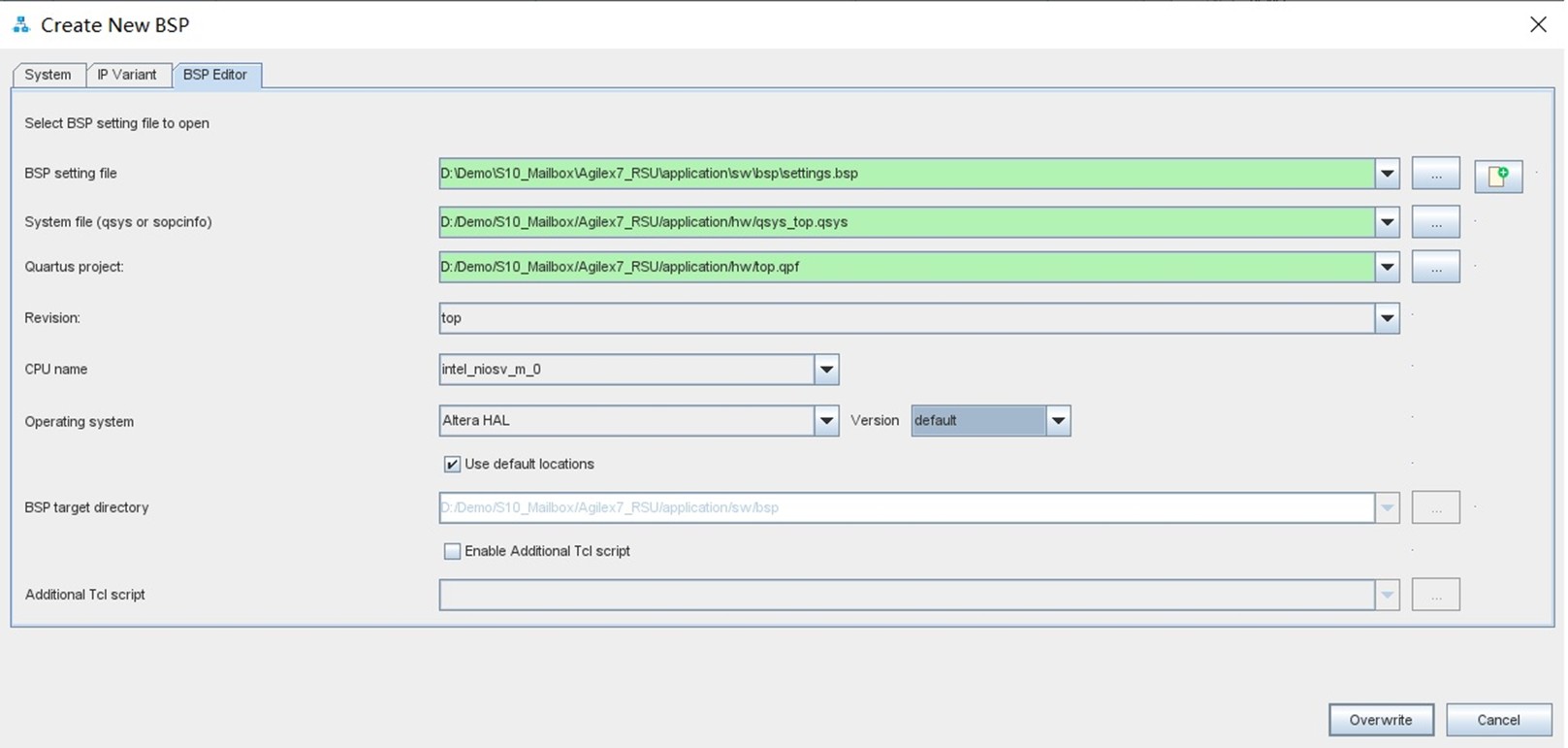

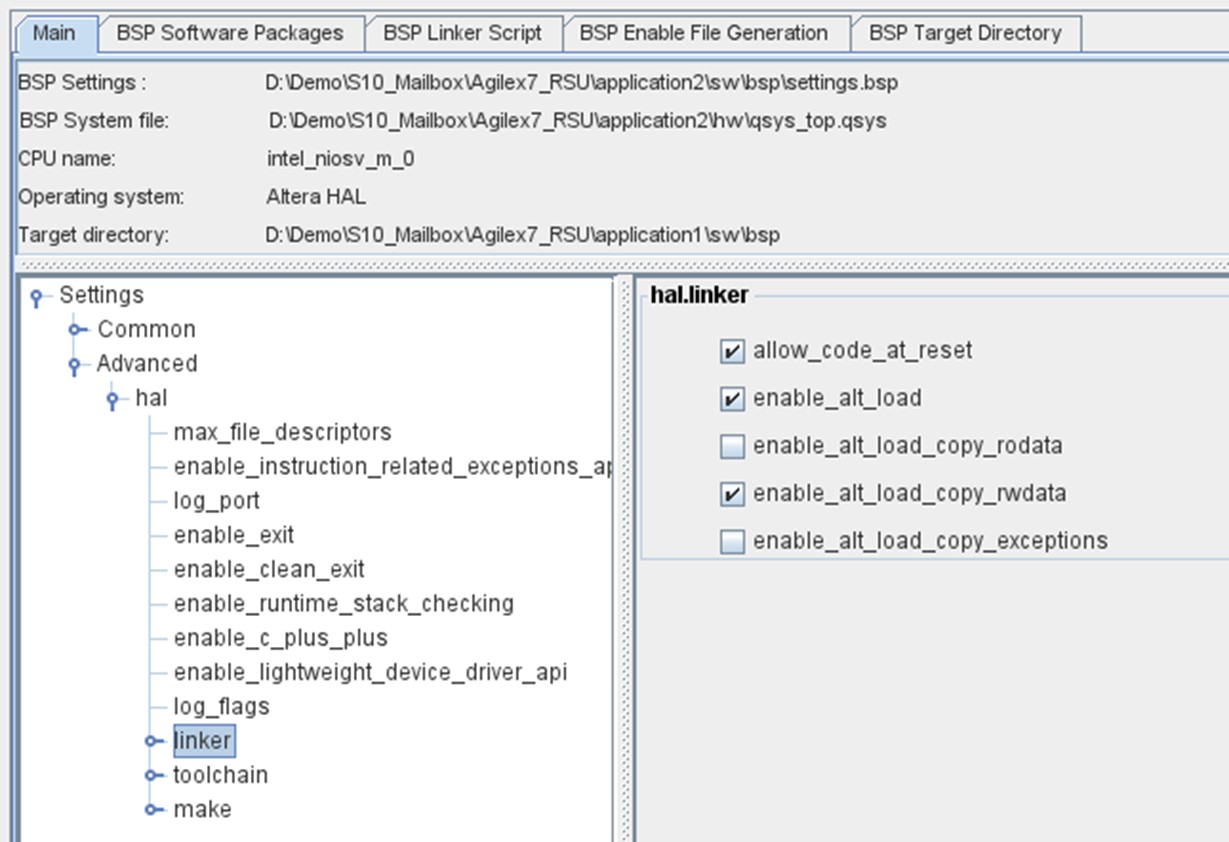

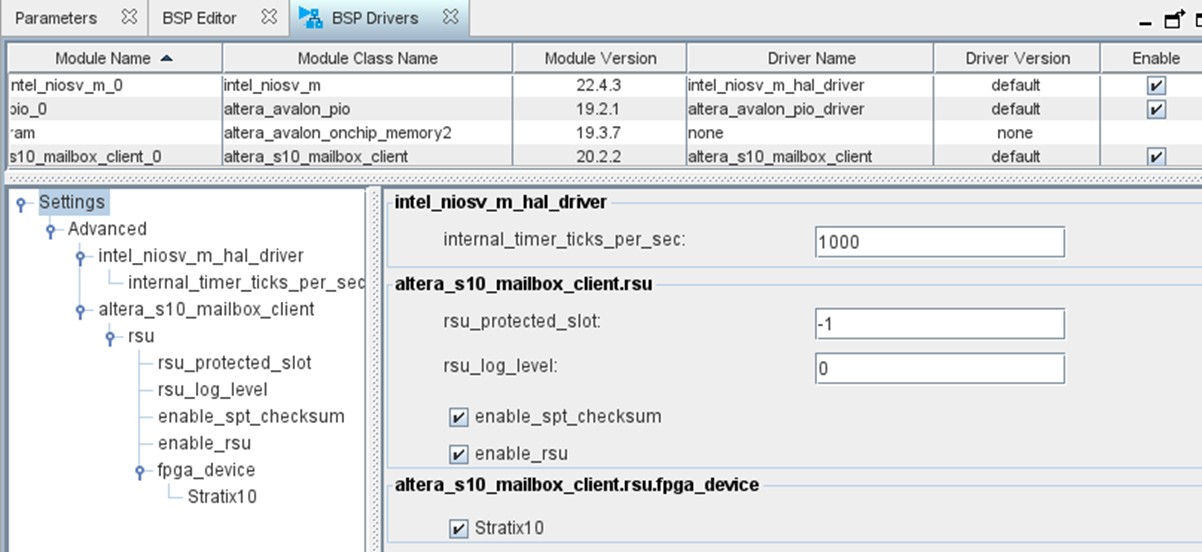

(7) 创建 BSP (board support package) 项目后,分别对 New BSP Window、hal.linker 和 BSP Drivers Tab 进行设置,如下图 (图9)、(图10)、(图11)、(图12) 所示:

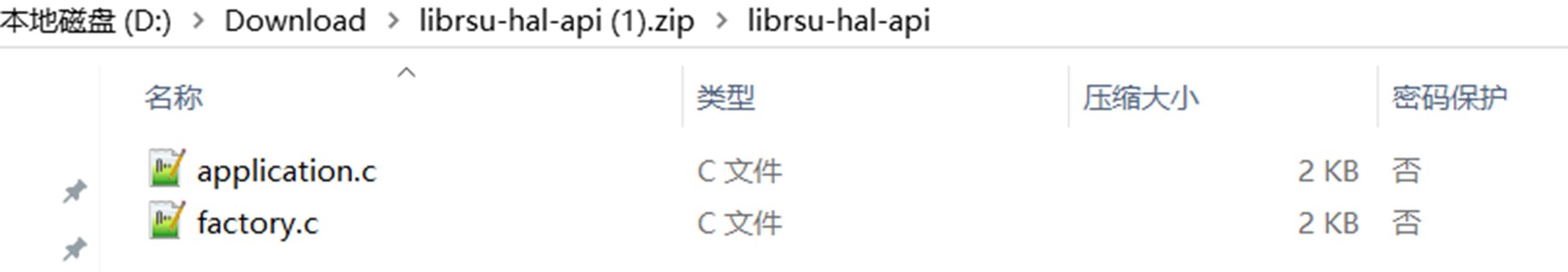

(8) 下载 Example source code for Nios® V Processor LibRSU application,放入 SW -> app 目录下。

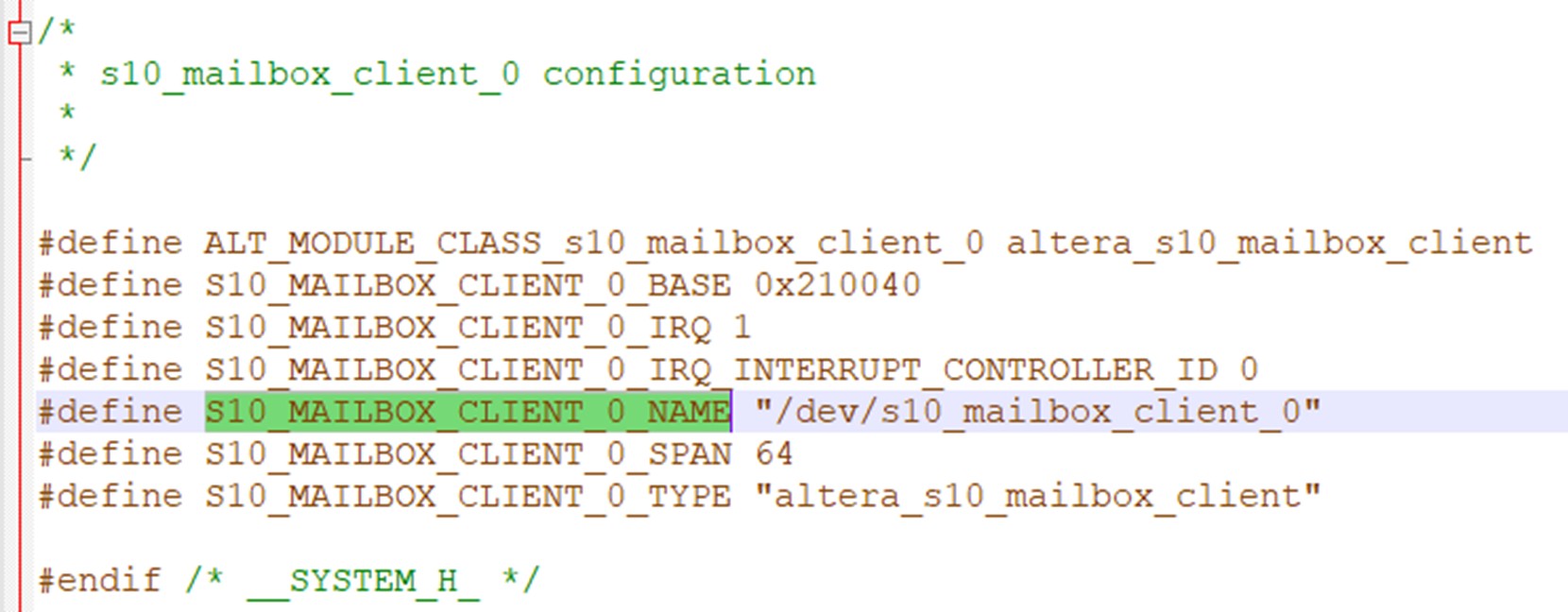

(9) 根据 BSP -> system.h 文件修改“Mailbox Client Altera FPGA IP (MAILBOX_NAME)”的默认名称,具体位置如下:

主程序中打开 mailbox:fd = mailbox_client_open (S10_MAILBOX_CLIENT_0_NAME) bsp/drivers/src/altera_s10_mailbox_client_flash_rsu.c bsp/drivers/src/altera_s10_mailbox_client_rsu.c

另外,需要注意,如果 Qsys 架构发生变化,BSP 需要重新生成。

(10) 在 Nios® V command shell 切换目录到工程目录下,执行下面的命令来生成用户应用程序 CMakeLists.txt。

niosv-app --app-dir=software/app --bsp-dir=software/bsp --srcs=software/app/application.c,zlib/crc32.c --incs=zlib

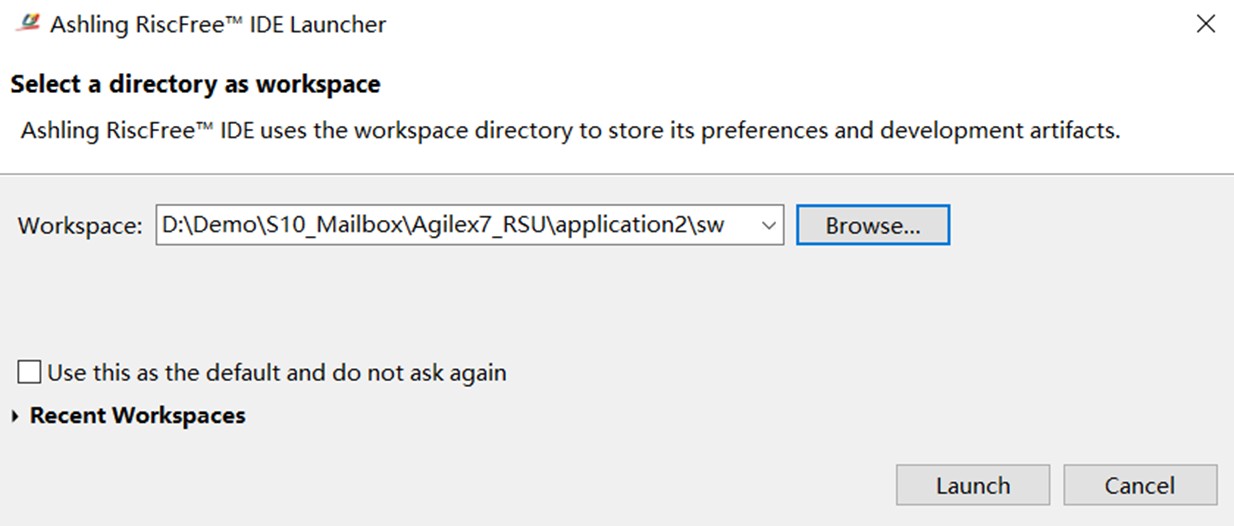

(11) 采用 RiscFree IDE 创建工程,编译生成 elf 文件。新建工程可参考《Ashling* RiscFree* Integrated Development Environment (IDE) for Intel® FPGAs User Guide》文档第 4 章。

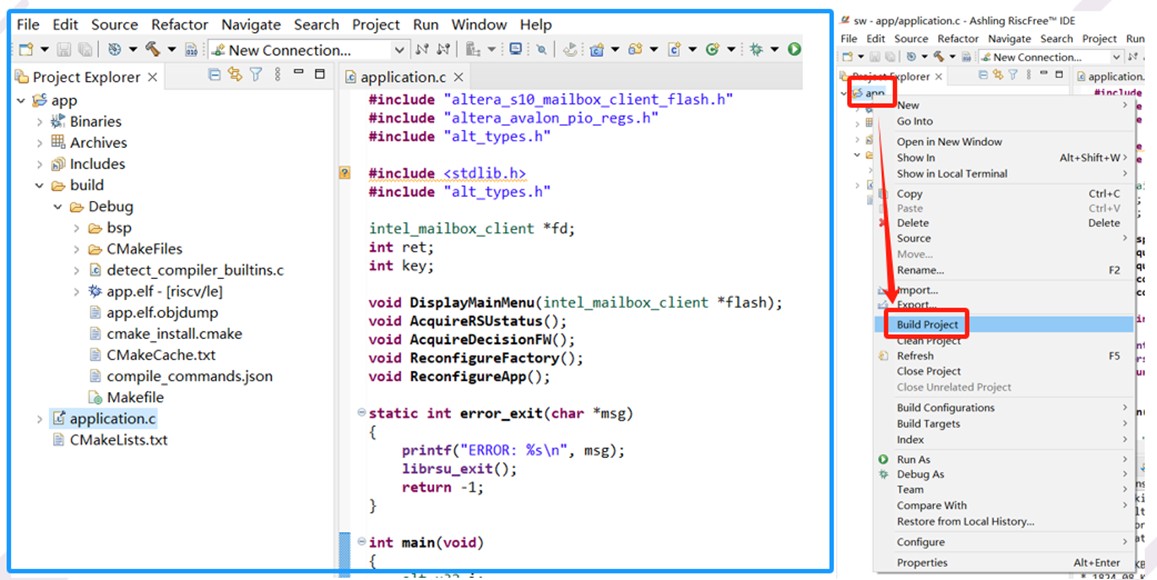

(12) 下图 (图16) 左边蓝色方框标记为创建的工程结构,接下来按照图片右边红色标记:右键 app -> Build project -> 生成 elf。

(13) 将 elf 文件转 hex 文件指令。其中有两个地方需要注意:

- 0x0-0x3ffff 为 hex 文件大小,这里取决于 c 代码的复杂程度,要完整放入 on-chip memory 中

- app.hex 文件需要在 Qsys 中的 on-chip memory 指定,当 hex 改变后重新生成 HDL

elf2hex software/app/build/Debug/app.elf -o app.hex -b 0x0 -w 32 -e 0x3ffff

(14) 在线烧写 elf 文件到 Nios® V 中指令,方便调试。

niosv-download -g -r sw/app/build/Debug/app.elf

(15) 当使能 jtag-uart 模块,在Nios® V command shell 中可以打印出 printf 信息。

juart-terminal

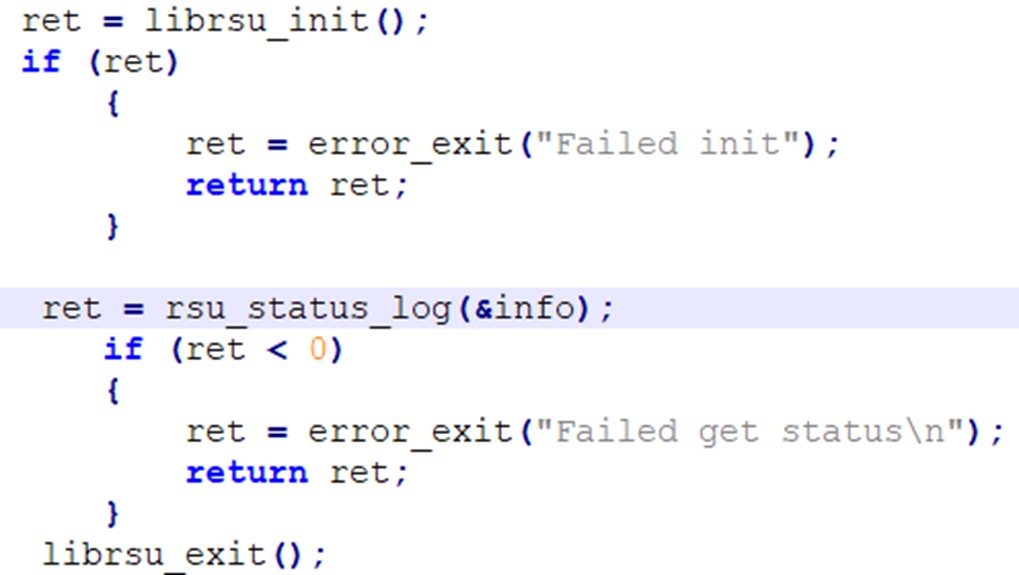

Nios® V 操作镜像切换

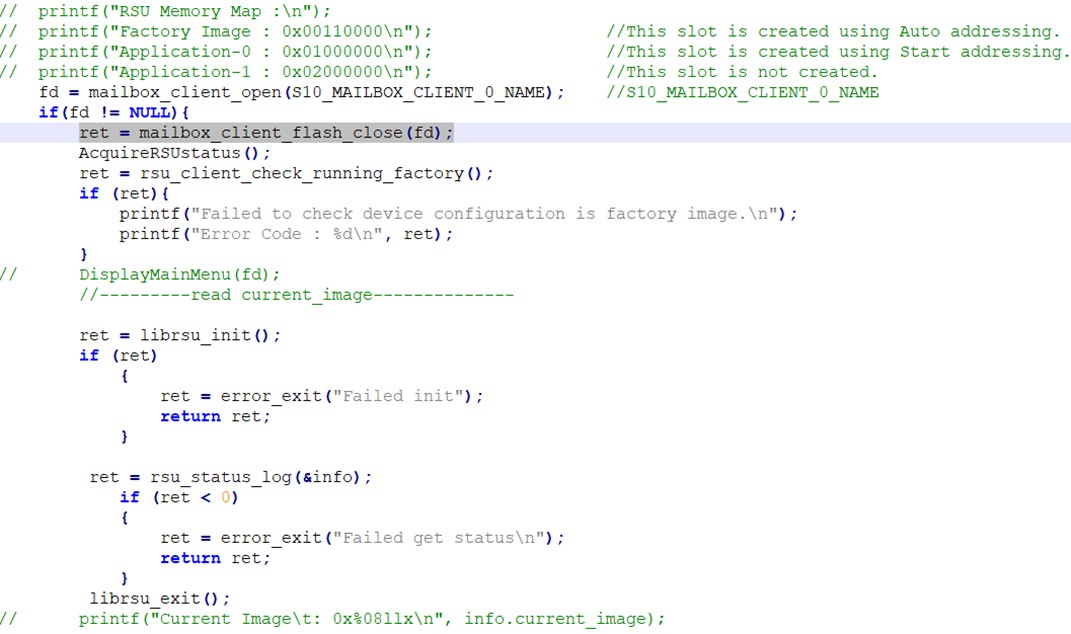

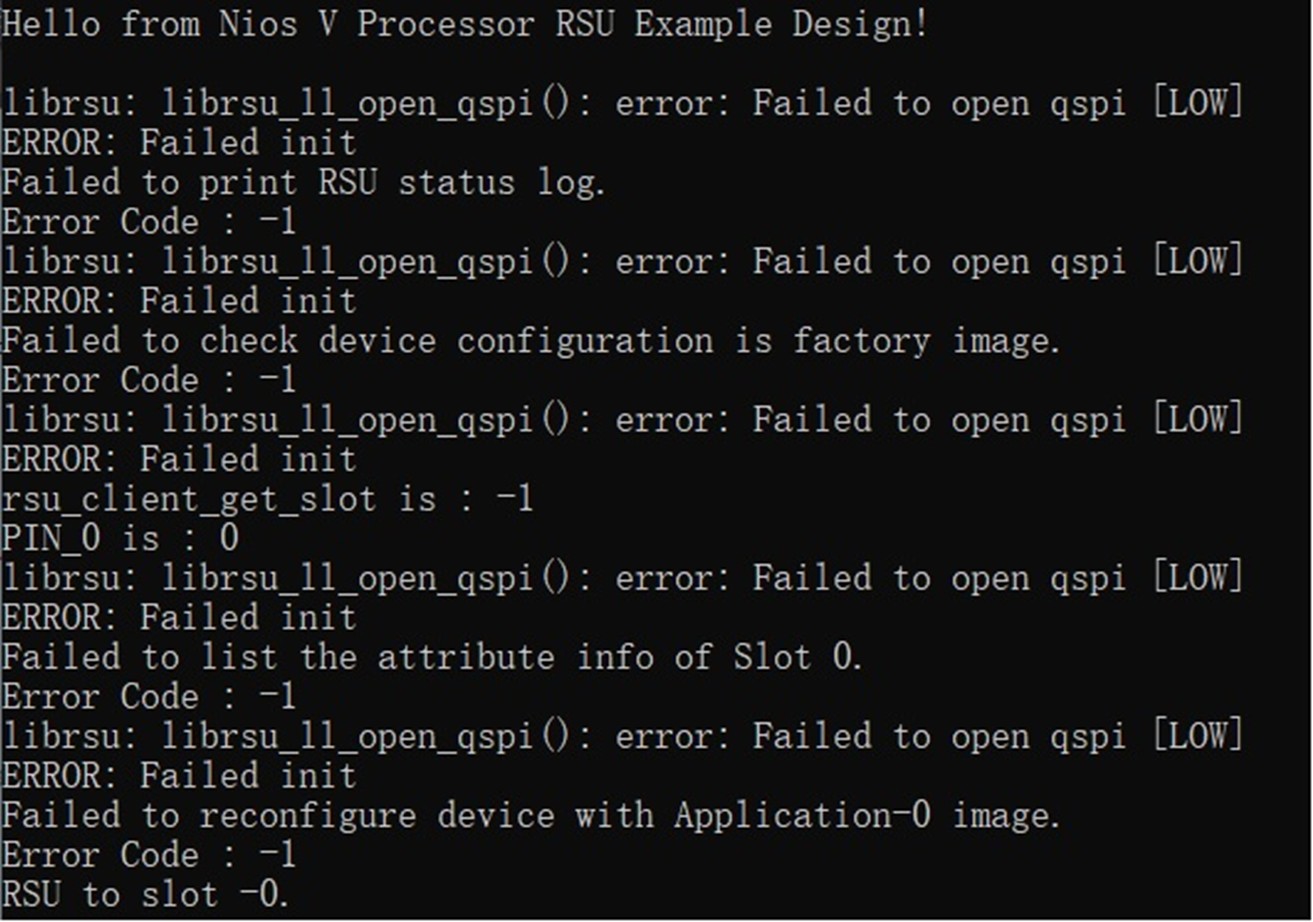

(1) 在 App 代码中,需要先关闭 QSPI flash,否则会出现如下图 (图18) 无法打开 QSPI 的报错,这是由于上一次切换操作没有关闭 flash 导致的。

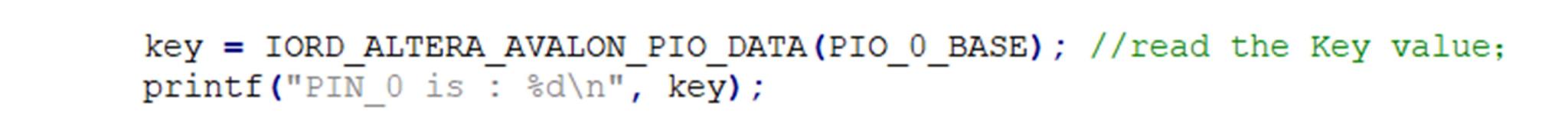

(2) 按键输入通过如下代码读回,这里的 PIO_0_BASE,也是根据 system.h 对 PIO 的定义。

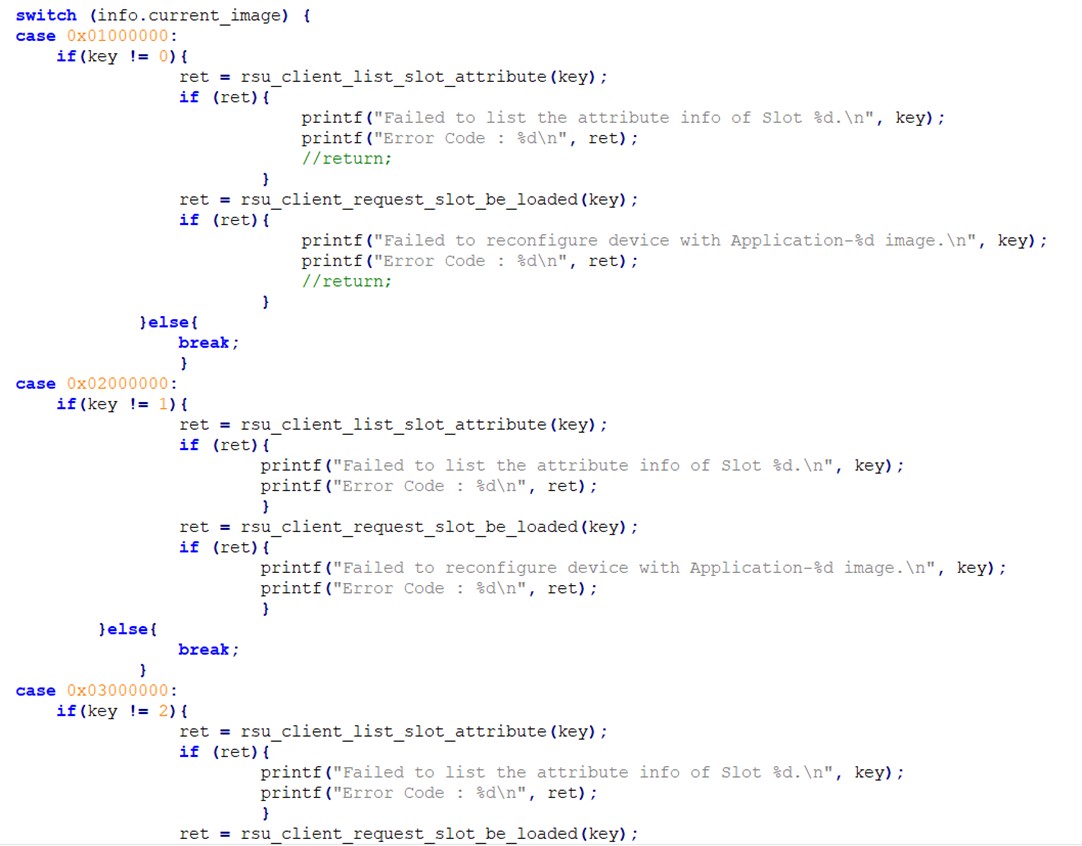

(3) 如下图 (图20) 所示,切换镜像操作。此时可以通过 info.current_image 确认当前镜像地址。

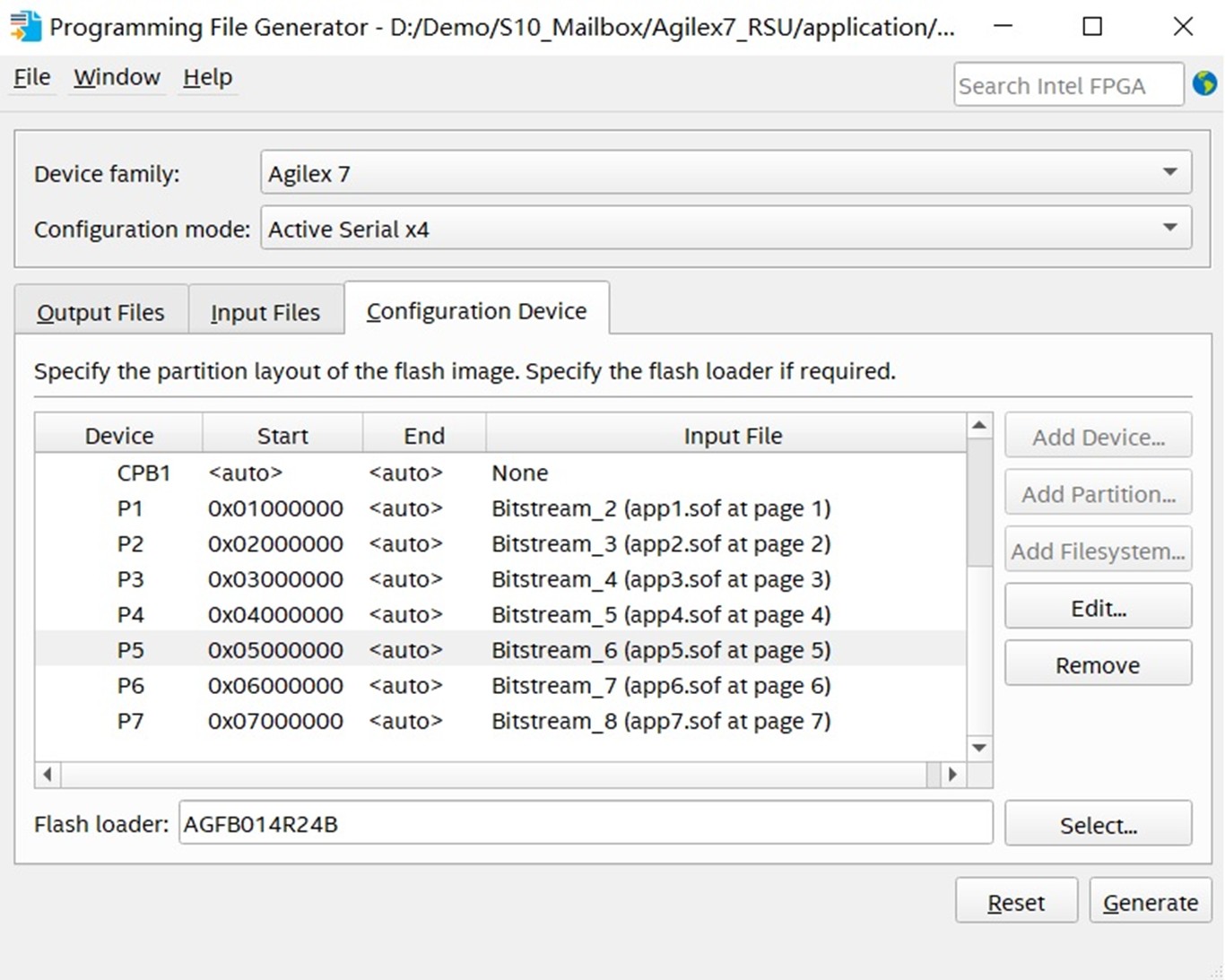

(4) 除了出厂镜像,目前 Quartus 支持添加 7 个镜像文件,每个镜像的地址可以手动输入。完整的 jic 生成过程参考《Nios® V Embedded Processor Design Handbook》7.3.4.1 节。

总结

本文主要介绍了在 Altera Agilex® 7 FPGA 平台上,通过 Nios® V 软核处理器操作 Mailbox Client IP 实现 FPGA 多镜像切换的参考方案。欲了解更多 Altera 相关方案或技术信息,可点击下方「联系我们」,提交您的需求,骏龙科技公司愿意为您提供更详细的技术解答。

参考资料

1. Altera Agilex® 7 FPGA - 使用 QSPI 闪存访问和远程系统更新的邮箱客户端设计示例

2. Mailbox Client Intel FPGA IP User Guide

3. Nios® V Embedded Processor Design Handbook

4. Ashling* RiscFree* Integrated Development Environment (IDE) for Intel® FPGAs User Guide

相关阅读

《基于 Nios® V 处理器的 Agilex®7 Mailbox Client IP 应用实践 (下) — 读取芯片 ID 和温度》