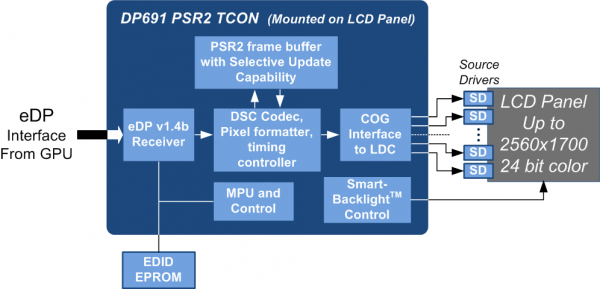

DP691 – 4 LANE EDP 1.4B PSR2 TCON

eDP v1.4b LCD Timing Controller with PSR2 and Integrated Frame Buffer, Up To 2560×1700 Resolution

DP691 supports the PSR2 protocol in the Embedded DisplayPort Standard version 1.4b. The device enables a new level of power reduction by supporting all eDP 1.4b power saving features including PSR2 with Selective Update, Advanced Link Power Management (ALPM), and VESA Display Stream Compression (DSC).

Features

- Supports display resolutions up to 2560×1700

- Compliant to VESA Embedded DisplayPort Standard version 1.4b

- Supports PSR and PSR2 with Selective Update

- Supports VESA Display Stream Compression (DSC) v1.1

- Includes backlight control through AUX

- 1.62 and 2.7Gbps eDP link operation with 1, 2, or 4 lanes

- CrystalFree™ technology; no external clock reference required

- Supports full and fast link training, and no link training

- Up to 24 color bit depth RGB format eDP input

- 6 or 8 component bit depth point-to-point SOC panel interface

- Media optimized playback modes

- Color Engine, FRC, and Gamma Correction with EEPROM for LUT storage

- Media optimized playback modes

- Programmable BIST and aging patterns

- Parade’s exclusive Smart-Backlight™ dynamic backlight control for color and power optimization

- Supports DisplayPort™ standard SSC 0.5% down spreading and additional spreading on Source Driver interface

- Supports VESA Adaptive-Sync

- Supports eDP DRR/nvDPS/sDRRS power saving modes

- ASSR display authentication support

- ESD HBM 8kV

- 5x12mm QFN RoHs Halogen free package

Applications

- High-Resolution COG LCD Panels for Mobile PC and AIO platforms

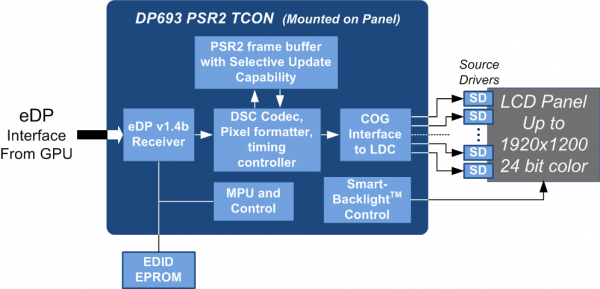

DP693 – 2 LANE EDP 1.4B PSR2 TCON

eDP v1.4b LCD Timing Controller with PSR2 and Integrated Frame Buffer, Up To 1920×1200 Resolution

DP693 supports the PSR2 protocol in the Embedded DisplayPort Standard version 1.4b. The device enables a new level of power reduction by supporting all eDP 1.4b power saving features including PSR2 with Selective Update, Advanced Link Power Management (ALPM), and VESA Display Stream Compression (DSC).

Features

- Supports display resolutions up to 1920×1200

- Compliant to VESA Embedded DisplayPort Standard version 1.4b

- Supports PSR and PSR2 with Selective Update

- Supports VESA Display Stream Compression (DSC) v1.1

- Includes backlight control through AUX

- 1.62 and 2.7Gbps eDP link operation with 1 or 2 lanes

- CrystalFree™ technology; no external clock reference required

- Supports full and fast link training, and no link training

- Up to 24 color bit depth RGB format eDP input

- 6 or 8 component bit depth point-to-point SOC panel interface

- Media optimized playback modes

- Color Engine, FRC, and Gamma Correction with EEPROM for LUT storage

- Media optimized playback modes

- Programmable BIST and aging patterns

- Parade’s exclusive Smart-Backlight™ dynamic backlight control for color and power optimization

- Supports DisplayPort™ standard SSC 0.5% down spreading and additional spreading on Source Driver interface

- Supports VESA Adaptive-Sync

- Supports eDP DRR/nvDPS/sDRRS power saving modes

- ASSR display authentication support

- ESD HBM 8kV

- 5x10mm QFN RoHs Halogen free package

Applications

- Full HD COG LCD Panels for Mobile PC and AIO platforms

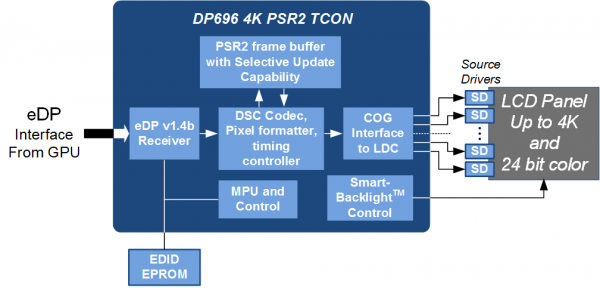

DP696 – 4 LANE 4K EDP PSR2 TCON

eDP v1.4b LCD Timing Controller with PSR2 and Integrated Frame Buffer, Up To 4K Resolution

DP696 supports the PSR2 protocol in the Embedded DisplayPort Standard version 1.4b. The device enables a new level of power reduction for 4K embedded displays by supporting all eDP 1.4b power saving features including PSR2 with Selective Update, Advanced Link Power Management (ALPM), and VESA Display Stream Compression (DSC).

Features

- Supports display resolutions up to 4096×2160 and 3840×2560

- Two chips can be sychronised to support higher resolutions including 7680×2160 or 5120×2880 (PSR or PSR2 cannot be used for 2 chip configuration)

- Supports a-Si, Oxide, and LTPS LCD panels including dual and triple gate and Z-inversion pixel structure

- Compliant to VESA Embedded DisplayPort Standard version 1.4b

- Supports PSR and PSR2 with Selective Update

- Supports VESA Display Stream Compression (DSC) v1.1

- Supports Parade’s SIPI® (Scalable Intra Panel Interface) CoG interface with 6 or 8 component bit depth

- Includes backlight control through AUX

- 1.62 and 2.7Gbps eDP link operation with 1, 2, or 4 lanes

- Up to 24 color bit depth RGB format eDP input

- Supports full and fast link training, and no link training

- CrystalFree™ technology; no external clock reference required

- Media optimized playback modes

- Supports VESA Adaptive-Sync, Free Sync, and G-Sync

- Color Engine, FRC, and Gamma Correction with EEPROM for LUT storage

- Programmable BIST and aging patterns

- Full programmable row and column driver control I/O

- Parade’s exclusive Smart-Backlight™ dynamic backlight control for color and power optimization

- Supports DisplayPort™ standard SSC 0.5% down spreading and additional spreading on Source Driver interface

- Supports eDP DRR/nvDPS/sDRRS power saving modes

- ASSR display authentication support

- ESD HBM 8kV

- 5x13mm WFBGA RoHs Halogen free package

Applications

- Ultra high resolution a-Si, Oxide, and LTPS LCD panels