EtherCAT Master Chip (Virtual ASSP) Solution

- Performance Advantages

- Shorter Cycle, able to reach 31.25us

- Fewer jitter, jitter time less than 0.04us

- Good synchronization performance, master and each slave devices are able to reach clock synchronization accuracy which is less than 1us (4-axis measurement 50ns)

- EtherCAT Master vASSP Order Model Number and Specifications:

EtherCAT Master vASSP Order Model Number Bus Type Data Bit Width Address Bus Bus Speed Applicable Processor 10M08SCU169I7G (PROGB) Address bus/ data bus reuse, asynchronous 16 digits 16 digits (reuse with data bus) 50 MHz Embedded processor 10M08SCU169I7G (PROGC) Address bus/ data bus independent, asynchronous 16 digits 16 digits 100 MHz Embedded processor 10M08SCU169I7G (PROGD) Address bus/ data bus independent, asynchronous 32 digits 16 digits 50 MHz PCIE Interface (only supports CH368 chip)

EtherCAT Master vASSP Development Board

- Main Chip: 10M08SCU169I7G(PROGB) + STM32F407

- 5V Power supply

- Provide full set development software source code

- Support PC end debug interface communicates with the board through the serial port

- Free to borrow

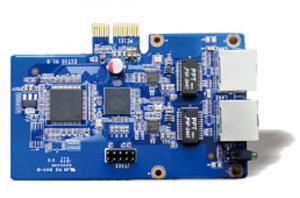

EtherCAT Master PCIE Acceleration Card

- Main Chip: 10M08SCU169I7G(PROGB) + CH368DS1

- Support PCIE x 1 interface

- Provide Linux + Xenomai driver source for Linux + Xenomai real-time system

- Order Model Number: ECTLAN

For details of Macnica Cytech’s products and solutions, please contact the company’s regional offices, or send emails to stonemao@macnica.com